# MiCOM P40 Agile

# 5th Generation P54

Technical Manual Single/Dual Breaker Current Differential with Distance

Hardware Version: Q Firmware Version: AB

Publication Reference: P54-TM-EN-2

#### Copyright statement

Copyright © 2024 GE Vernova. All rights reserved.

FlexLogic, FlexElement, FlexCurve, FlexAnalog, FlexInteger, FlexState, EnerVista, EnerVista Launchpad, and EnerVista D&I Setup software, CyberSentry, HardFiber, Universal Relay, Multilin, Multilin Agile, and GE Multilin are trademarks or registered trademarks of GE Vernova.

The contents of this manual are the property of GE Vernova. This documentation is furnished on license and may not be reproduced in whole or in part without the permission of GE Vernova. The content of this manual is for informational use only and is subject to change without notice.

#### **Disclaimer**

It is the responsibility of the user to verify and validate the suitability of all GE Vernova Grid Automation products. This equipment must be used within its design limits. The proper application including the configuration and setting of this product to suit the power system assets is the responsibility of the user, who is also required to ensure that all local or regional safety guidelines are adhered to. Incorrect application of this product could risk damage to property/the environment, personal injuries or fatalities and shall be the sole responsibility of the person/entity applying and qualifying the product for use.

The content of this document has been developed to provide guidance to properly install, configure and maintain this product for its intended applications. This guidance is not intended to cover every possible contingency that may arise during commissioning, operation, service, or maintenance activities. Should you encounter any circumstances not clearly addressed in this document, contact your local GE Vernova service site.

The information contained in this document is subject to change without notice.

IT IS THE SOLE RESPONSIBILITY OF THE USER TO SECURE THEIR NETWORK AND ASSOCIATED DEVICES AGAINST CYBER SECURITY INTRUSIONS OR ATTACKS. GE VERNOVA AND ITS AFFILIATES ARE NOT LIABLE FOR ANY DAMAGES AND/OR LOSSES ARISING FROM OR RELATED TO SUCH SECURITY INTRUSION OR ATTACKS.

4 P54-TM-EN-2

### Contents

| Chapte | er 1 Introduction                                                 | 1  |

|--------|-------------------------------------------------------------------|----|

| 1.1    | Chapter Overview                                                  |    |

| 1.2    | Foreword                                                          | 3  |

| 1.2.1  | Target Audience                                                   | 3  |

| 1.2.2  | Typographical Conventions                                         |    |

| 1.2.3  | Nomenclature                                                      | 4  |

| 1.2.4  | Compliance                                                        | 4  |

| 1.3    | Product Scope                                                     |    |

| 1.3.1  | Product Versions                                                  | Į  |

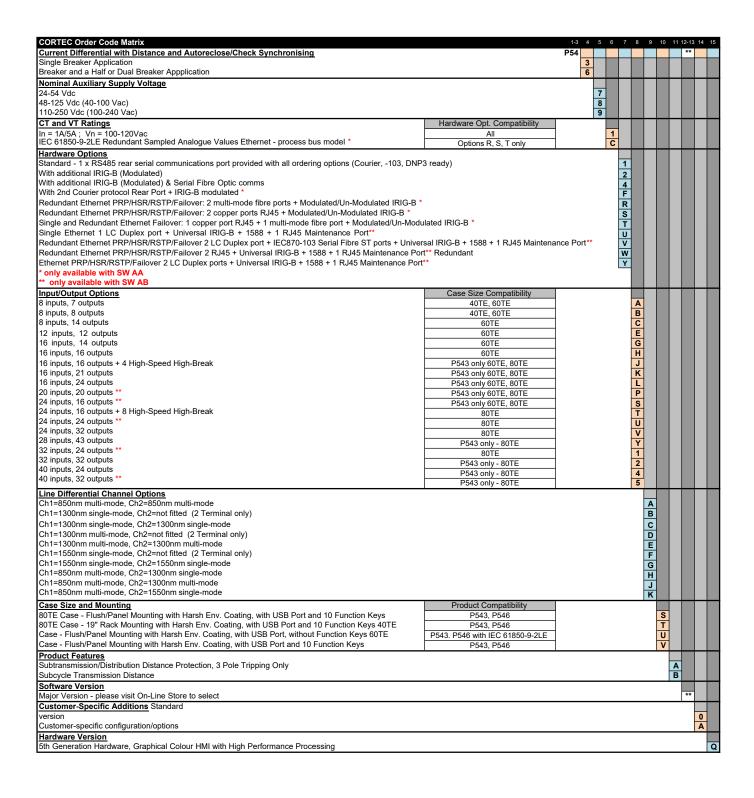

| 1.3.2  | Ordering Options                                                  | (  |

| 1.4    | Features and Functions                                            | 7  |

| 1.4.1  | Current Differential Protection Functions                         | -  |

| 1.4.2  | Distance Protection Functions                                     | -  |

| 1.4.3  | Protection Functions                                              | -  |

| 1.4.4  | Control Functions                                                 | 8  |

| 1.4.5  | Measurement Functions                                             | (  |

| 1.4.6  | Communication Functions                                           | (  |

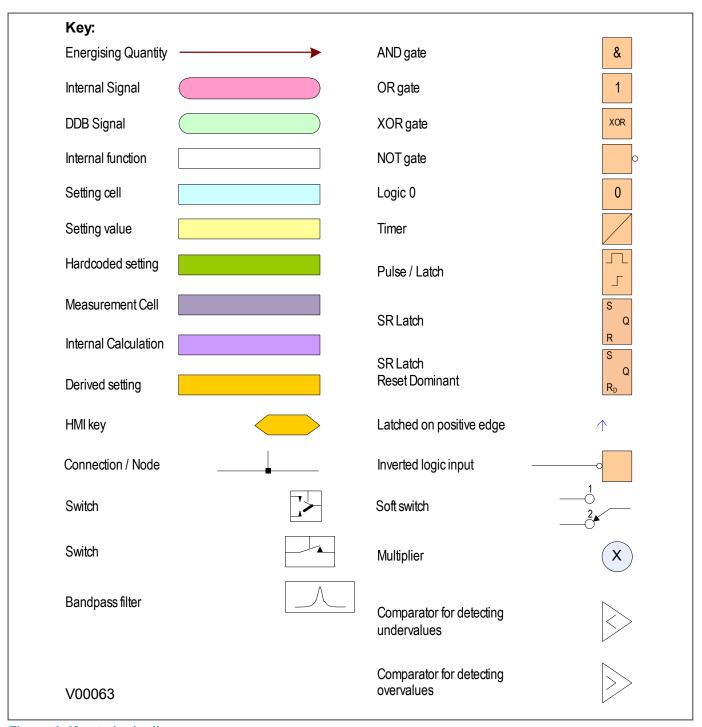

| 1.5    | Logic Diagrams                                                    | 10 |

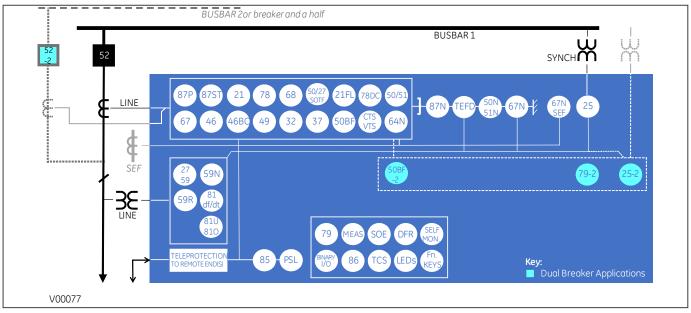

| 1.6    | Functional Overview                                               | 12 |

| Chapte | er 2 Safety Information                                           | 15 |

| 2.1    | Chapter Overview                                                  | 16 |

| 2.2    | Health and Safety                                                 | 17 |

| 2.3    | Symbols                                                           | 18 |

| 2.4    | Installation, Commissioning and Servicing                         | 19 |

| 2.4.1  | Lifting Hazards                                                   | 19 |

| 2.4.2  | Electrical Hazards                                                | 19 |

| 2.4.3  | UL/CSA/CUL Requirements                                           | 20 |

| 2.4.4  | Fusing Requirements                                               | 20 |

| 2.4.5  | Equipment Connections                                             | 2′ |

| 2.4.6  | Protection Class 1 Equipment Requirements                         | 2′ |

| 2.4.7  | Pre-energisation Checklist                                        | 22 |

| 2.4.8  | Peripheral Circuitry                                              | 22 |

| 2.4.9  | Upgrading/Servicing                                               | 24 |

| 2.5    | Decommissioning and Disposal                                      | 2  |

| 2.6    | Regulatory Compliance                                             | 26 |

| 2.6.1  | EMC Compliance: 2014/30/EU                                        | 26 |

| 2.6.2  | LVD Compliance: 2014/35/EU                                        | 26 |

| 2.6.3  | UL/CUL Compliance                                                 | 26 |

| 2.6.4  | UKCA Compliance                                                   | 26 |

| 2.6.5  | EMC Compliance: Electromagnetic Compatibility Regulations 2016    | 26 |

| 2.6.6  | Safety Compliance: Electrical Equipment (Safety) Regulations 2016 | 26 |

| 2.6.7  | Morocco Compliance                                                | 27 |

| 2.6.8  | EMC Compliance: No. 2574-14 of Ramadan 1436                       | 27 |

| 2.6.9  | Safety Compliance: No. 2573-14 of Ramadan 1436                    | 27 |

| Chapte | er 3 Hardware Design                                              | 29 |

| 3.1    | Chapter Overview                                                  | 30 |

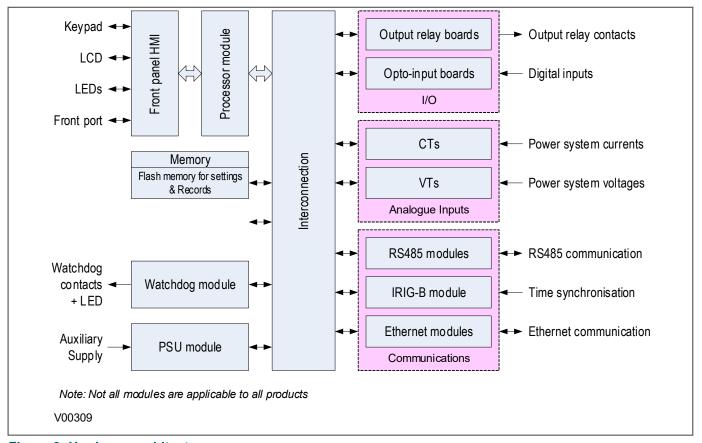

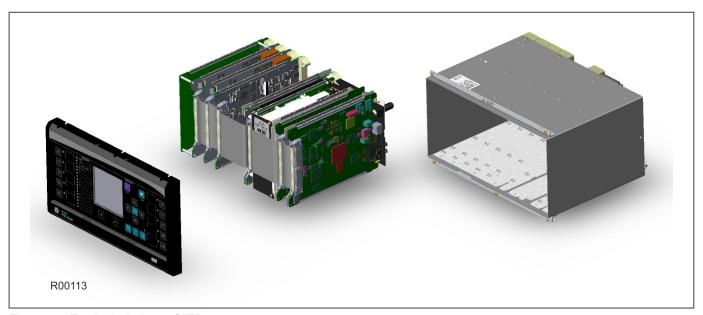

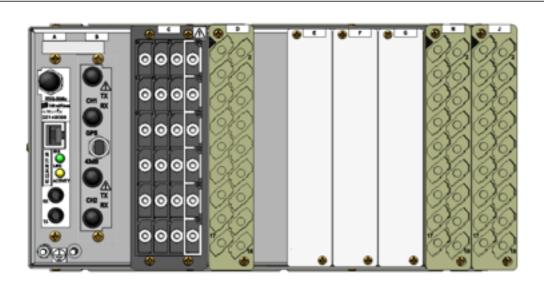

| 3.2    | Hardware Architecture                                             | 3′ |

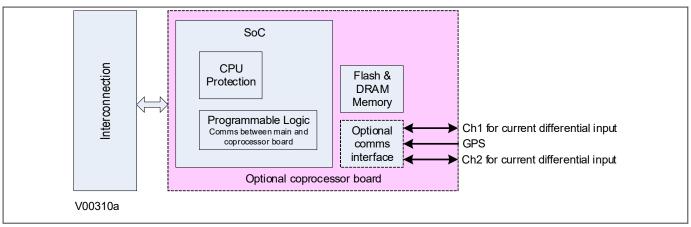

| 3.2.1  | Coprocessor Hardware Architecture                                 | 3′ |

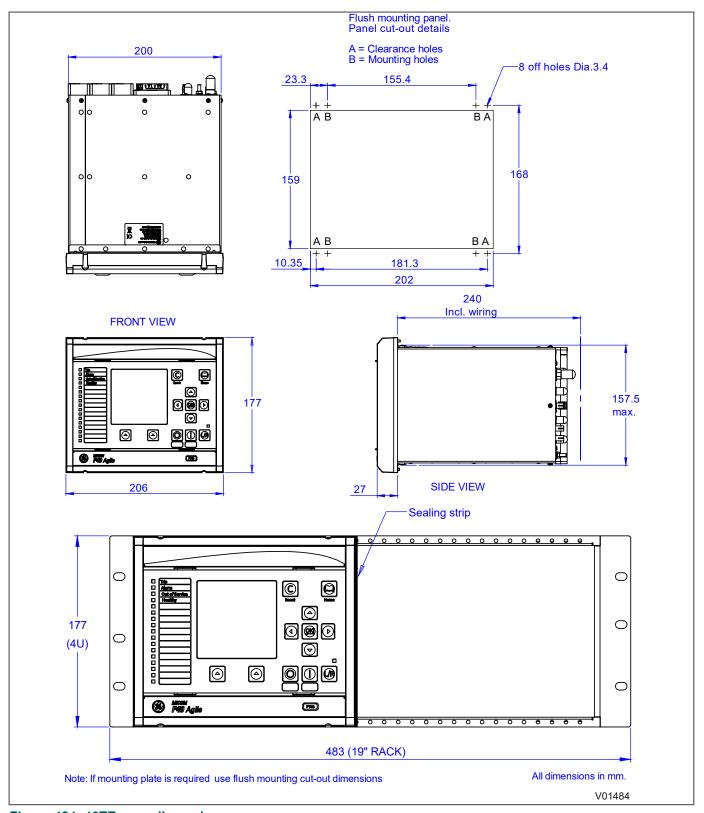

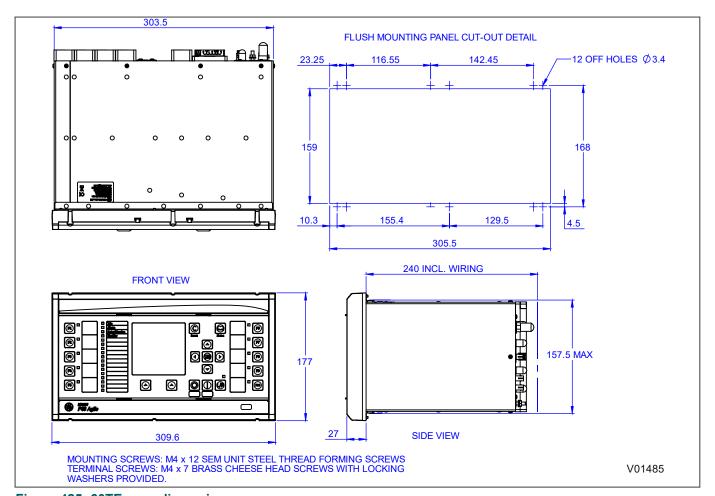

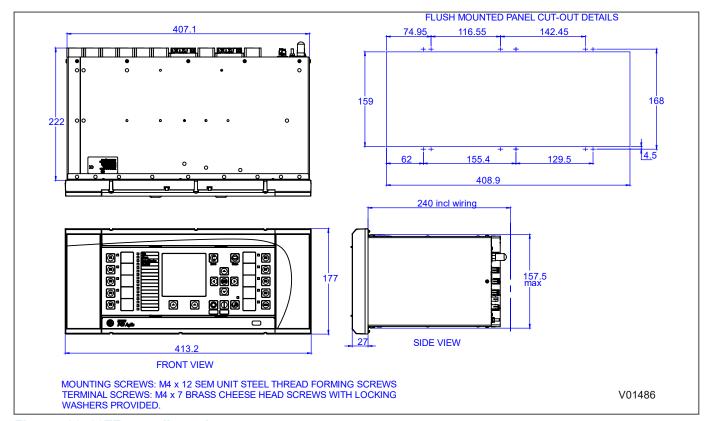

| 3.3    | Mechanical Implementation                                         | 33 |

| P | 54 |

|---|----|

|   | PS |

| 3.3.1              | Housing Variants                                                  | 33       |

|--------------------|-------------------------------------------------------------------|----------|

| 3.3.2              | List of Boards                                                    | 34       |

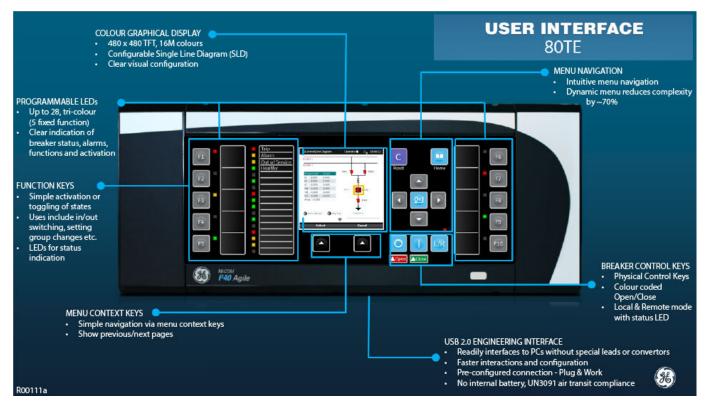

| 3.4                | Front Panel                                                       | 35       |

| 3.4.1              | Front Panel Compartments                                          | 35       |

| 3.4.2              | HMI Panel                                                         | 35       |

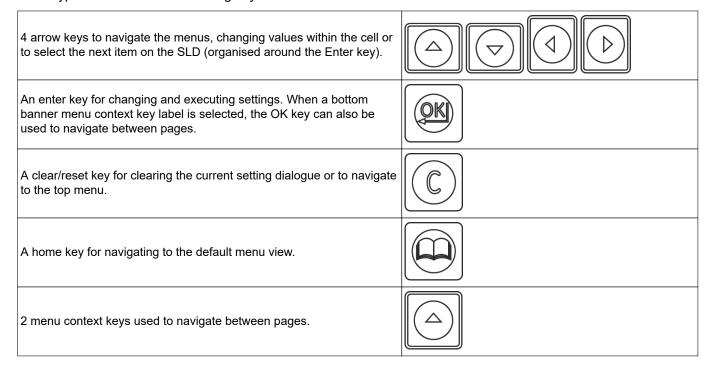

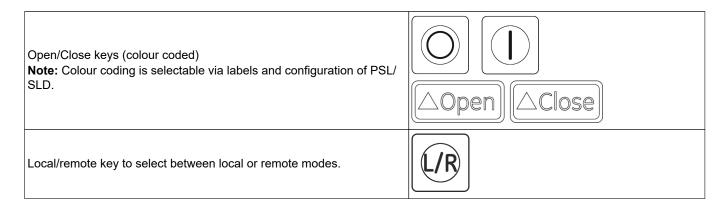

| 3.4.3              | Keypad                                                            | 36       |

| 3.4.4              | USB Port                                                          | 37       |

| 3.4.5              | Fixed Function LEDs                                               | 37       |

| 3.4.6              | Function Keys                                                     | 38       |

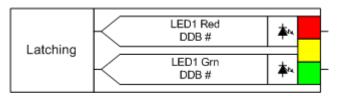

| 3.4.7              | Programable LEDs                                                  | 38       |

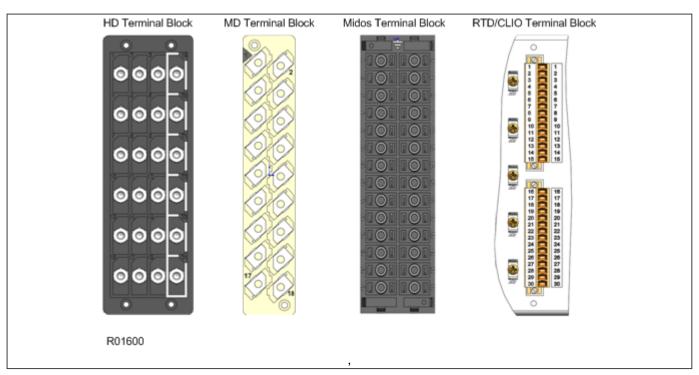

| 3.5                | Rear Panel                                                        | 39       |

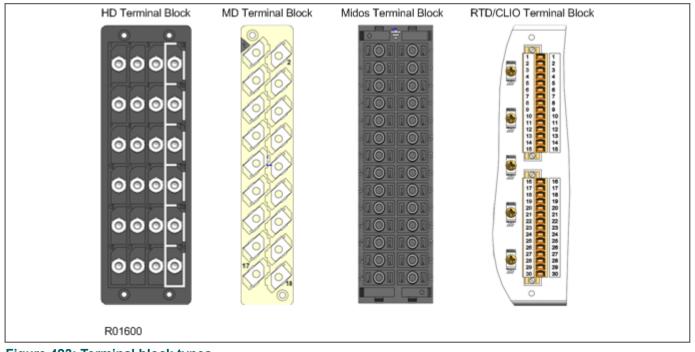

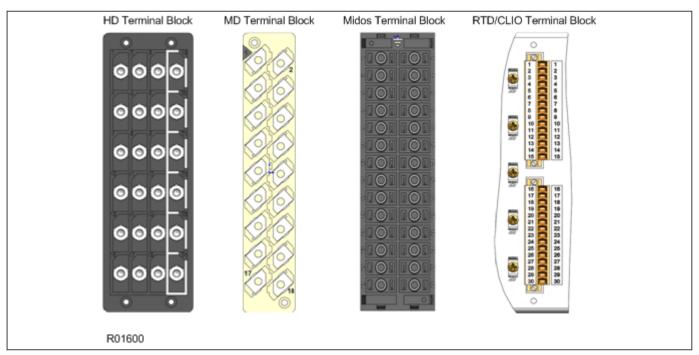

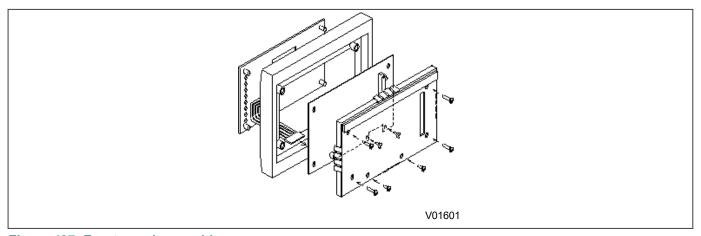

| 3.5.1              | Terminal Block Ingress Protection                                 | 40       |

| 3.6                | Boards and Modules                                                | 41       |

| 3.6.1              | PCBs                                                              | 41       |

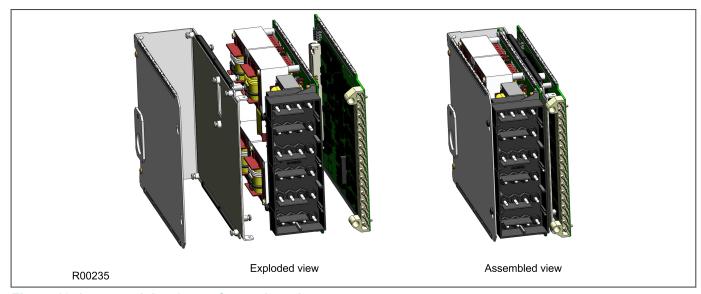

| 3.6.2              | Subassemblies                                                     | 41       |

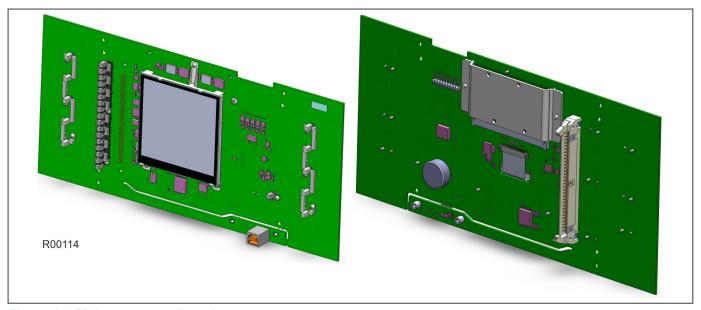

| 3.6.3              | Main Processor Board                                              | 42       |

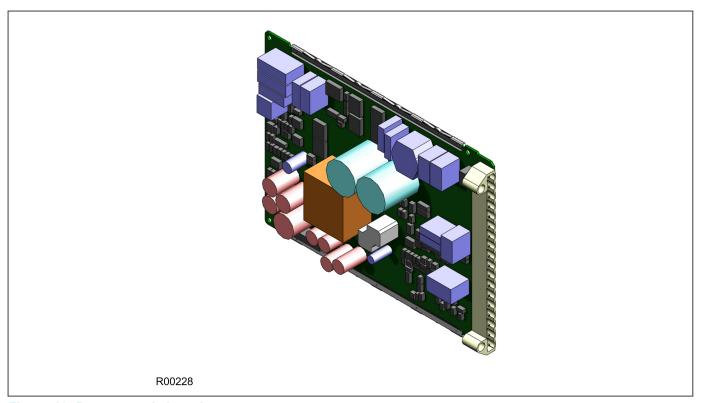

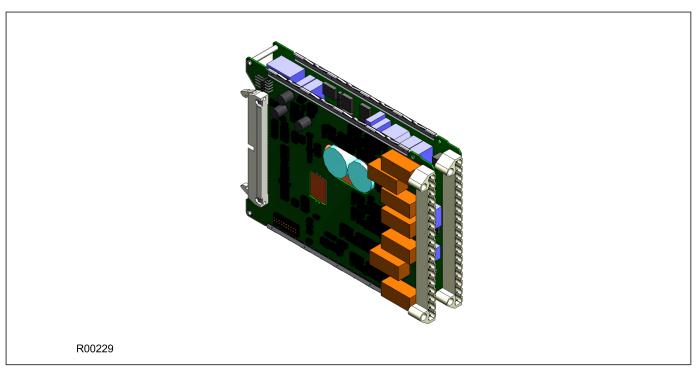

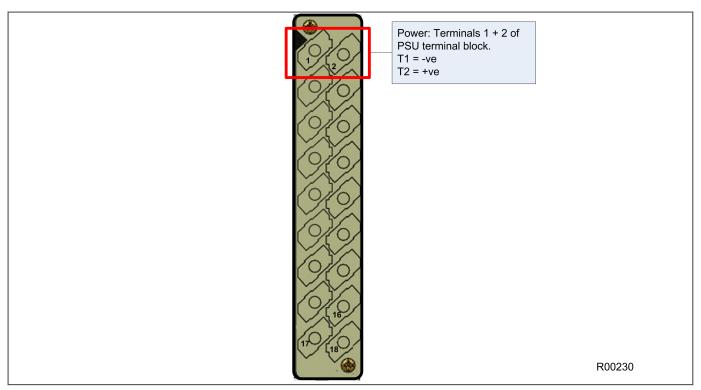

| 3.6.4              | Power Supply Board                                                | 43       |

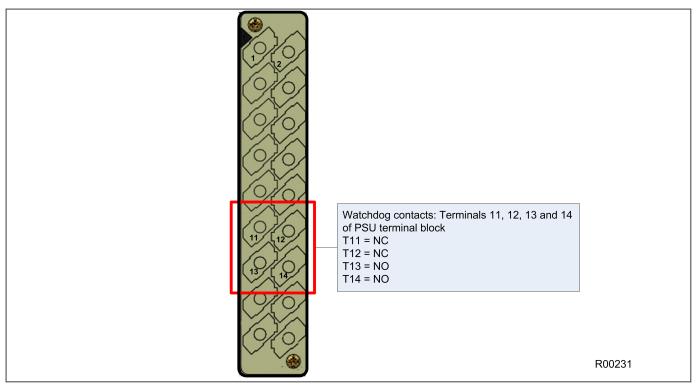

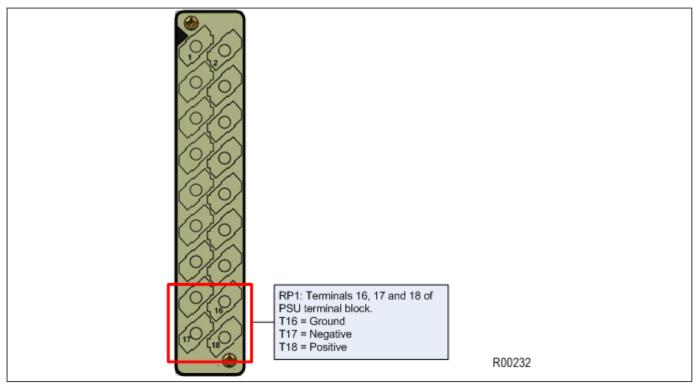

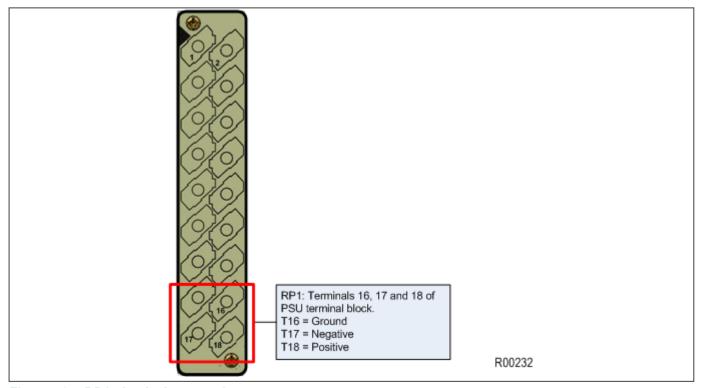

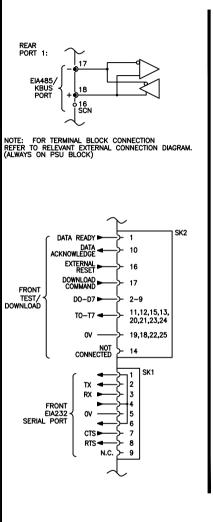

| 3.6.4.1<br>3.6.4.2 | Watchdog<br>Rear Serial Port                                      | 45<br>46 |

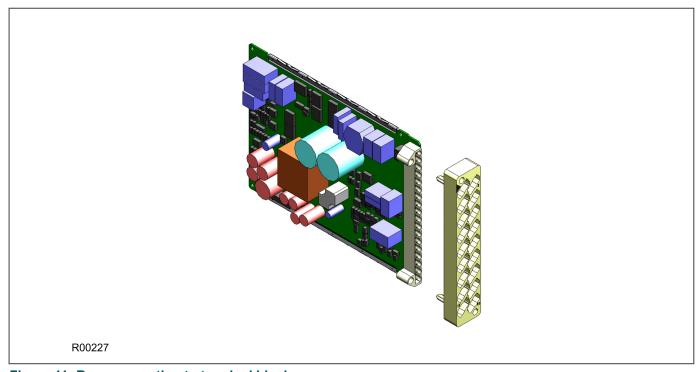

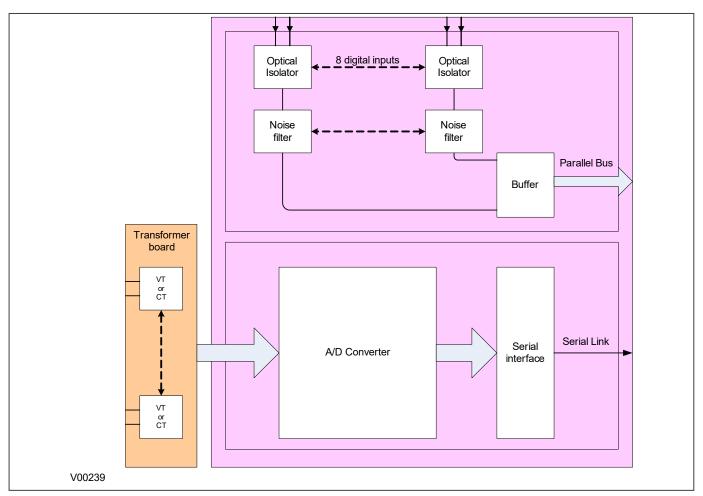

| 3.6.5              | Input Module - 1 Transformer Board                                | 47       |

| 3.6.5.1            | Input Module Circuit Description                                  | 48       |

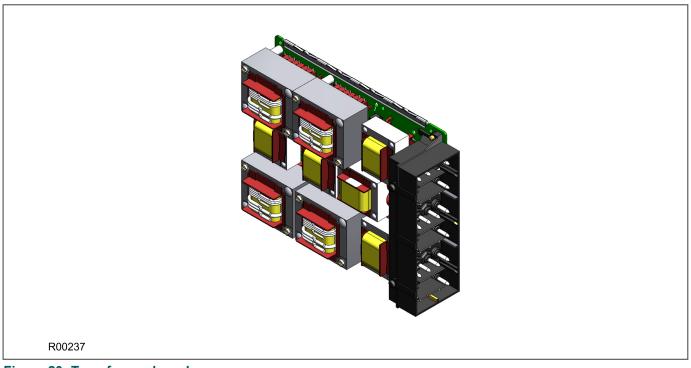

| 3.6.5.2            | Transformer Board                                                 | 49       |

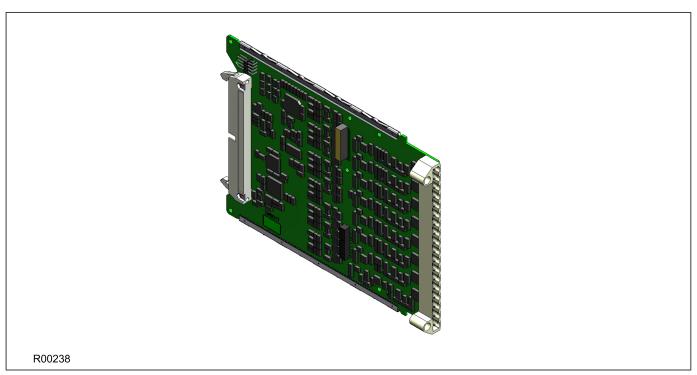

| 3.6.5.3            | Input Board                                                       | 50       |

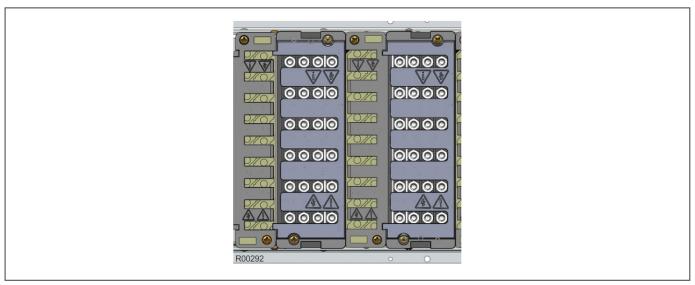

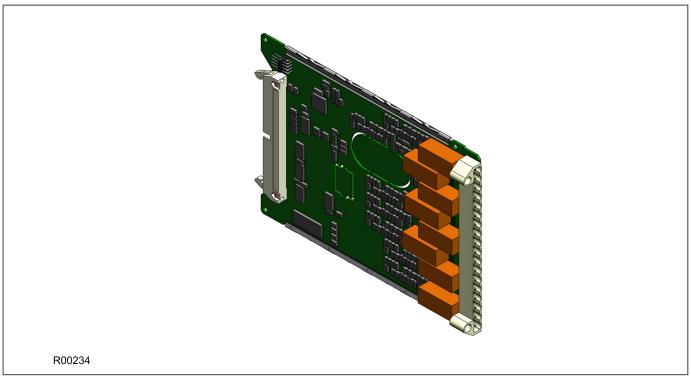

| 3.6.6              | Standard Output Relay Board                                       | 51       |

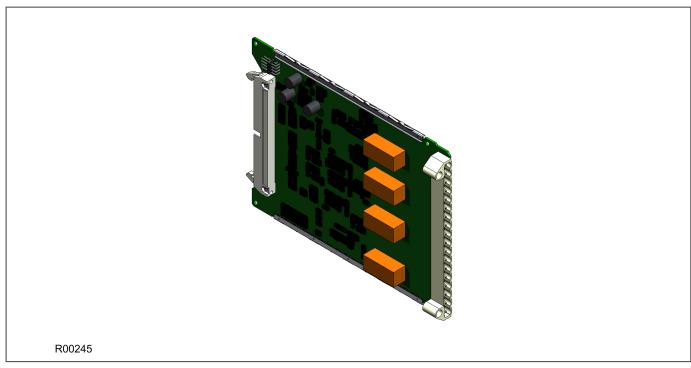

| 3.6.7              | High Break Output Relay Board                                     | 52       |

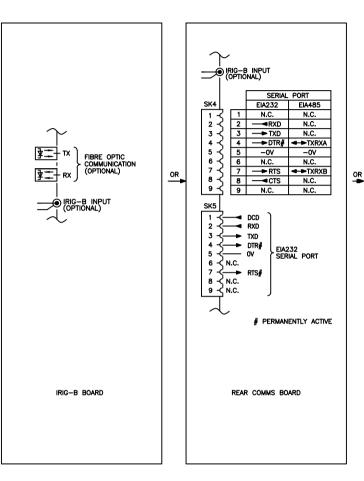

| 3.6.8              | IRIG-B Board                                                      | 54       |

| 3.6.9              | Fibre Optic Board                                                 | 55       |

| 3.6.10             | Rear Communication Board                                          | 56       |

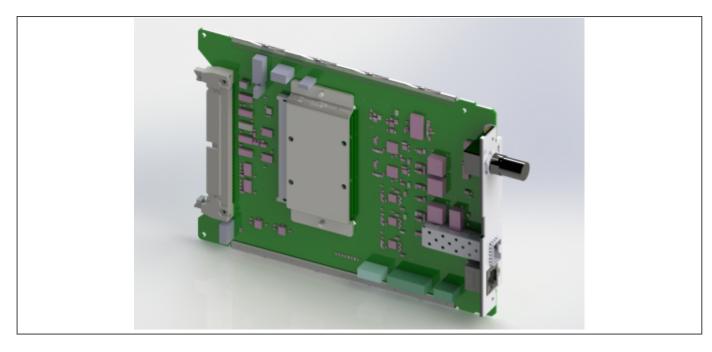

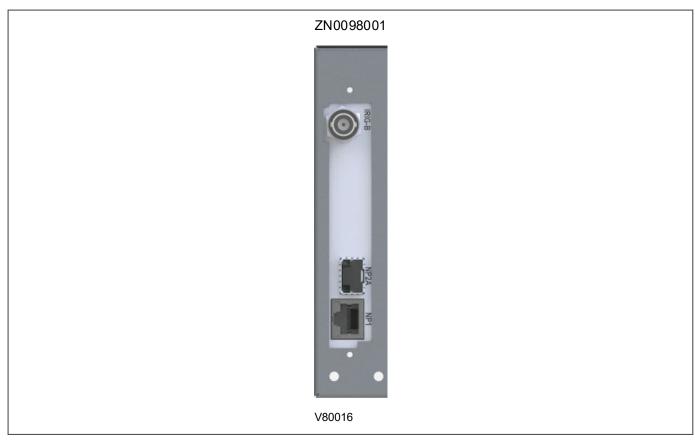

| 3.6.11             | Single Ethernet Board                                             | 56       |

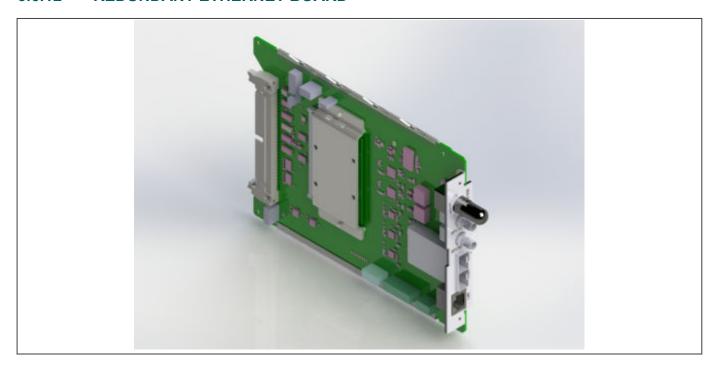

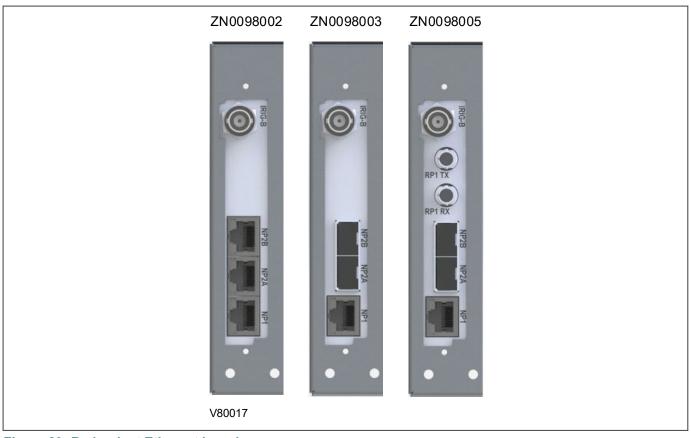

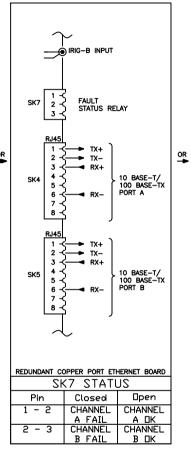

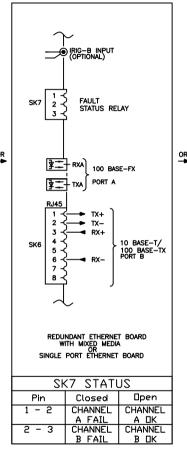

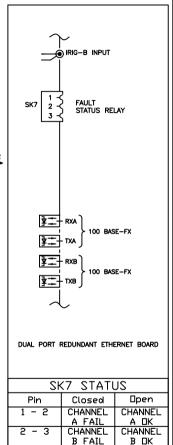

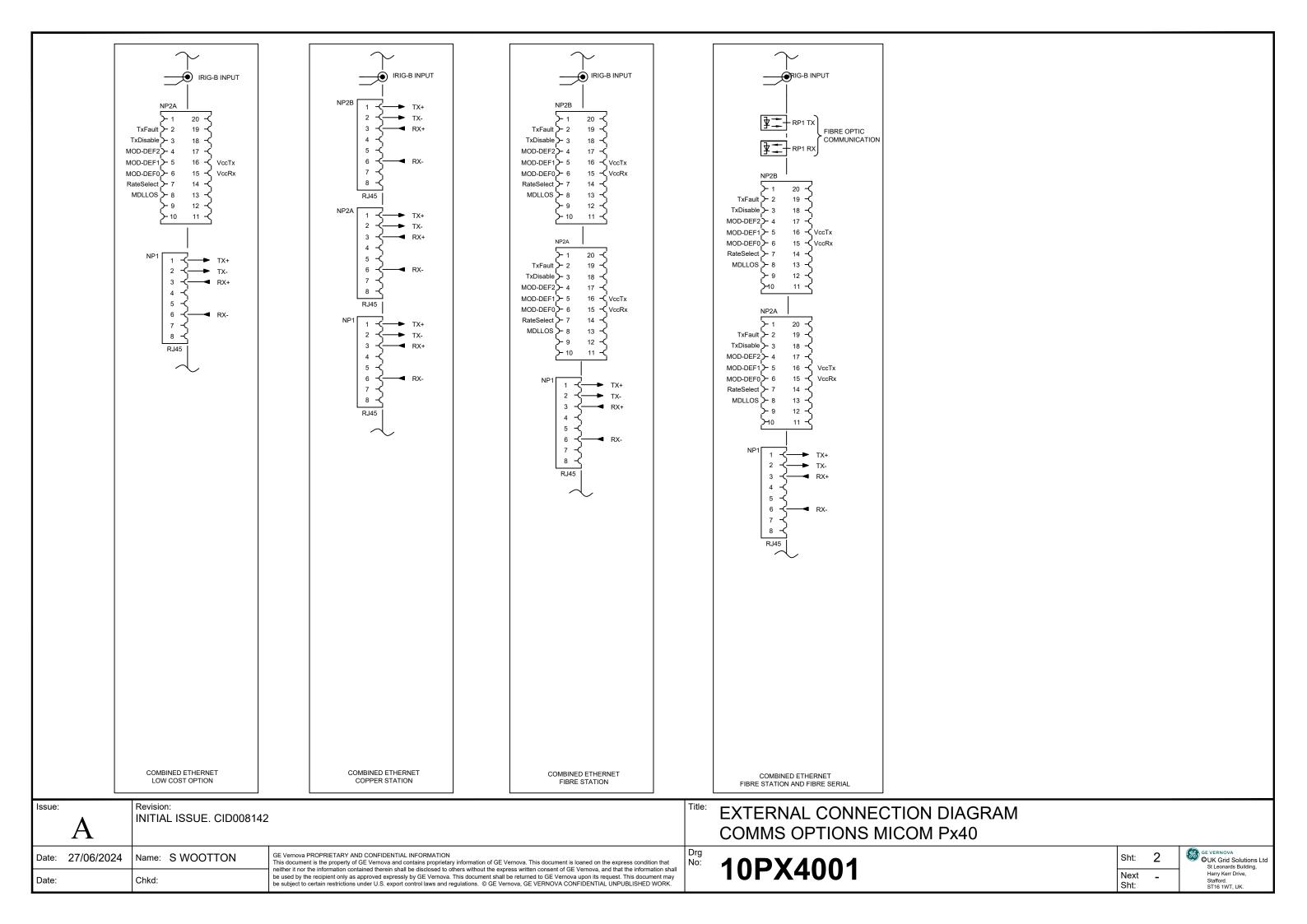

| 3.6.12             | Redundant Ethernet Board                                          | 58       |

| 3.6.13             | Coprocessor Board                                                 | 61       |

| 3.6.13.1           | Current Differential Inputs                                       | 61       |

| 3.6.13.2           | Coprocessor board with 1PPS input                                 | 62       |

| Chapte             | r 4 Software Design                                               | 63       |

| 4.1                | Chapter Overview                                                  | 64       |

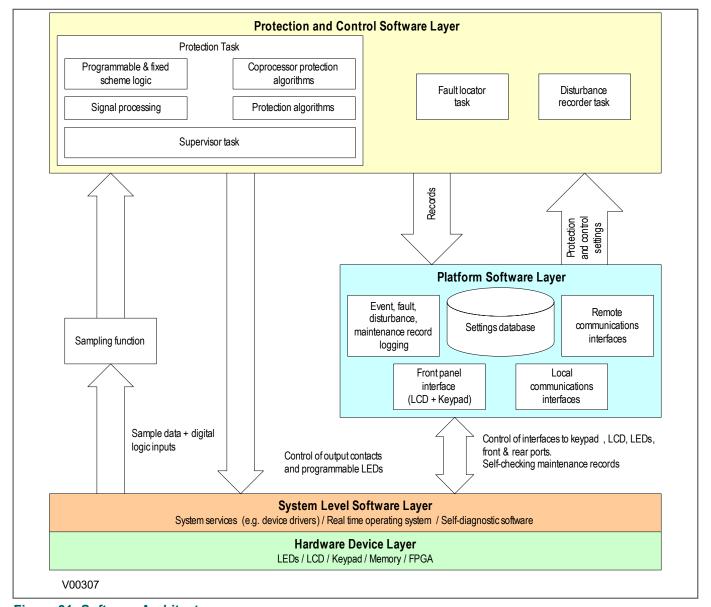

| 4.2                | Sofware Design Overview                                           | 65       |

| 4.3                | System Level Software                                             | 66       |

| 4.3.1              | Real Time Operating System                                        | 66       |

| 4.3.2              | System Services Software                                          | 66       |

| 4.3.3              | Self-Diagnostic Software                                          | 66       |

| 4.3.4              | Startup Self-Testing                                              | 66       |

| 4.3.4.1            | System Boot                                                       | 66       |

| 4.3.4.2            | System Level Software Initialisation                              | 67       |

| 4.3.4.3            | Platform Software Initialisation and Monitor                      |          |

| 4.3.5              | Continuous Self-Testing                                           | 67       |

| 4.4                | Platform Software                                                 | 69       |

| 4.4.1              | Record Logging                                                    | 69       |

| 4.4.2              | Settings Database                                                 | 69       |

| 4.4.3              | Interfaces                                                        | 69       |

| <b>4.5</b>         | Protection and Control Functions                                  | 70       |

| 4.5.1              | Acquisition of Samples                                            | 70       |

| 4.5.2              | Frequency Tracking                                                | 70       |

| 4.5.3<br>4.5.4     | Direct Use of Sampled Values System Level Software Initialisation | 70<br>70 |

| 4.5.4<br>4.5.5     | Distance Protection                                               | 70       |

| 7.5.5              | DISIGNOE FIOLECTION                                               |          |

ii P54-TM-EN-2

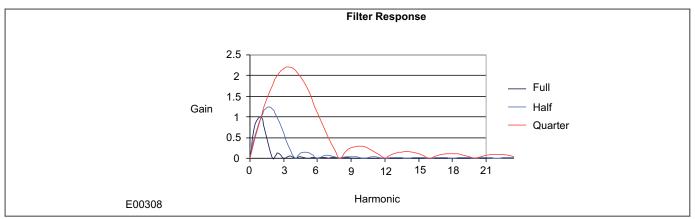

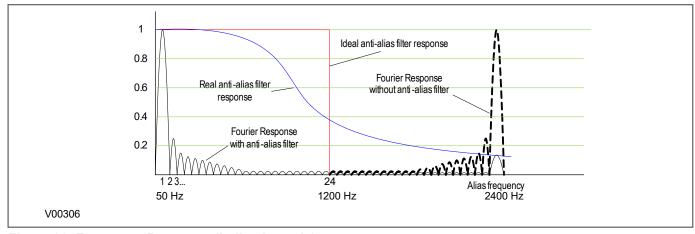

| 4.5.6               | Fourier Signal Processing                                                | 71                |

|---------------------|--------------------------------------------------------------------------|-------------------|

| 4.5.7               | Programmable Scheme Logic                                                | 72                |

| 4.5.8<br>4.5.9      | Event Recording Disturbance Recorder                                     | 72<br>73          |

| 4.5.9               | Fault Locator                                                            | 73                |

| 4.5.10              | Function Key Interface                                                   | 73                |

|                     |                                                                          |                   |

| Chapte              | r 5 Configuration                                                        | 75                |

| 5.1                 | Chapter Overview                                                         | 76                |

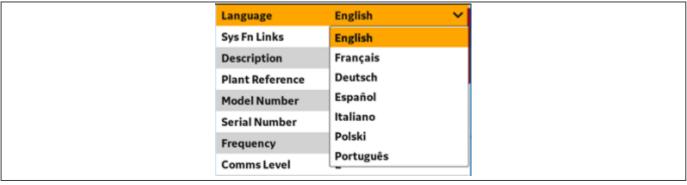

| 5.2                 | Settings Application Software                                            | 77                |

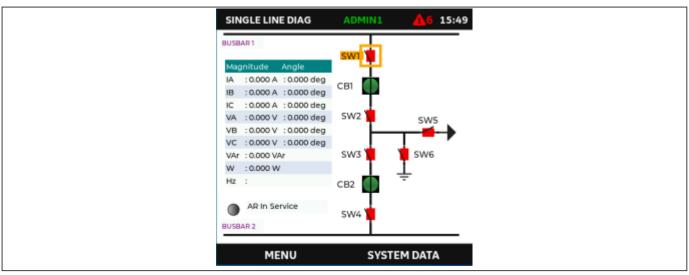

| 5.3                 | Using the HMI Panel                                                      | 78                |

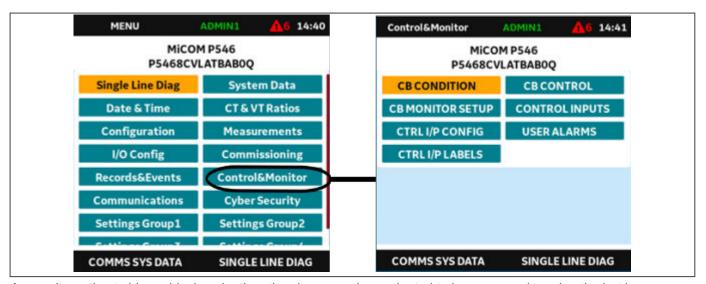

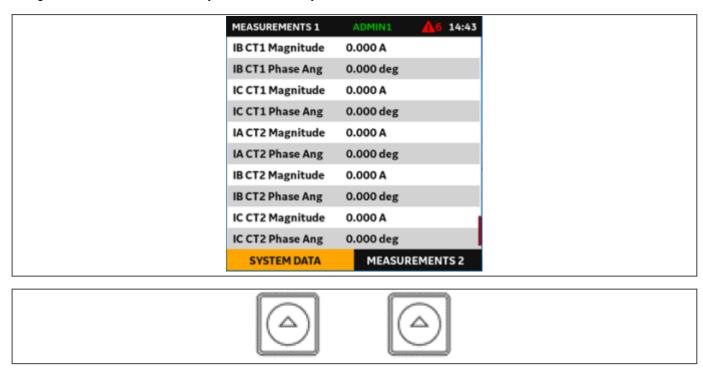

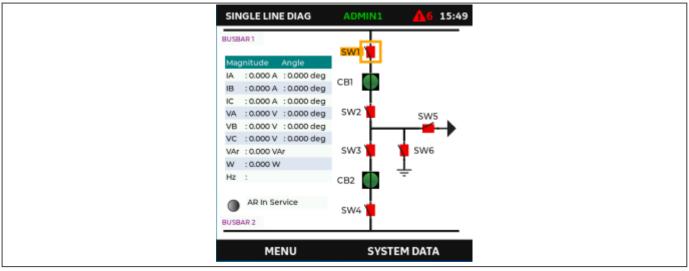

| 5.3.1               | Navigating the HMI Panel                                                 | 79                |

| 5.3.2               | Getting Started                                                          | 79                |

| 5.3.3               | Default Display                                                          | 79                |

| 5.3.4               | Default Display Navigation                                               | 80                |

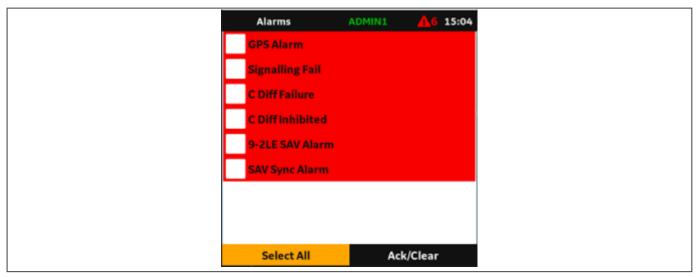

| 5.3.5               | Processing Alarms and Records                                            | 81                |

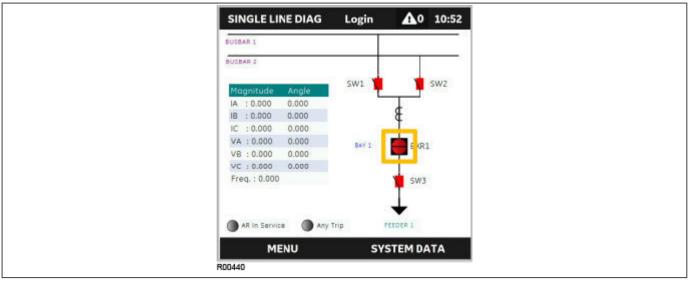

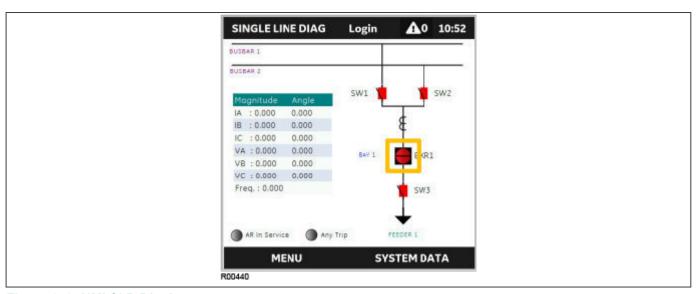

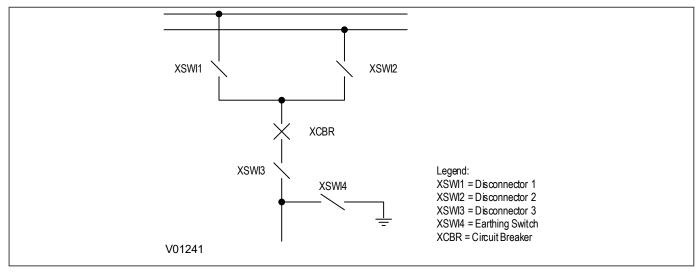

| 5.3.6<br>5.3.6.1    | Single Line Diagram (SLD) Viewer Circuit Breaker Control (SLD View Only) | 82<br>82          |

| 5.3.6.2             | Switch Control (SLD View Only)                                           | 83                |

| 5.3.7               | Menu Structure                                                           | 84                |

| 5.3.8               | Direct Access (Menu Context Keys)                                        | 85                |

| 5.3.8.1             | Control Inputs                                                           | 86                |

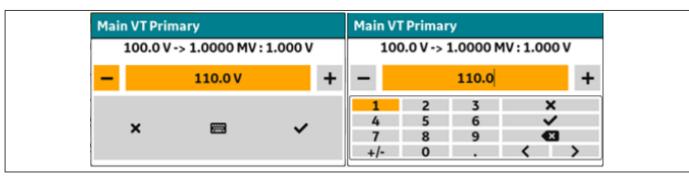

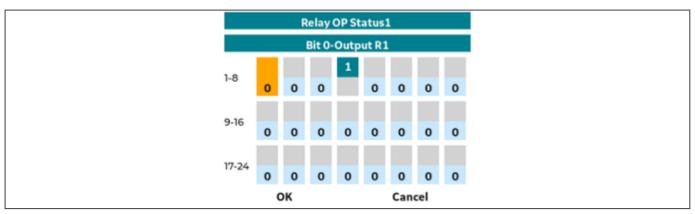

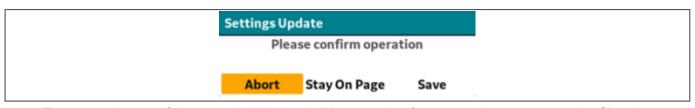

| 5.3.9               | Changing the Settings                                                    | 86                |

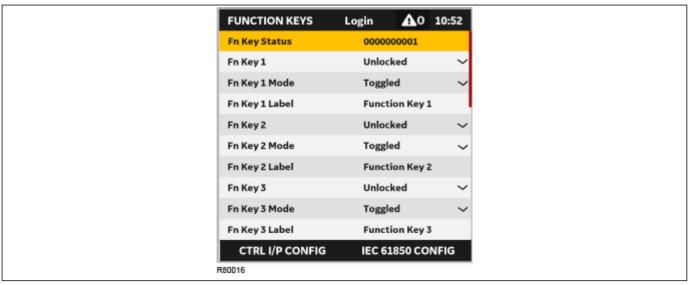

| 5.3.10              | Function Keys                                                            | 87                |

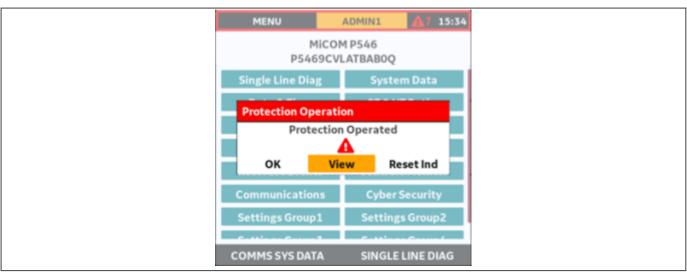

| 5.3.10.1            | Visualisation of Protection Operation                                    | 88                |

| Chapte              | r 6 Current Differential Protection                                      | 91                |

| 6.1                 | Chapter Overview                                                         | 92                |

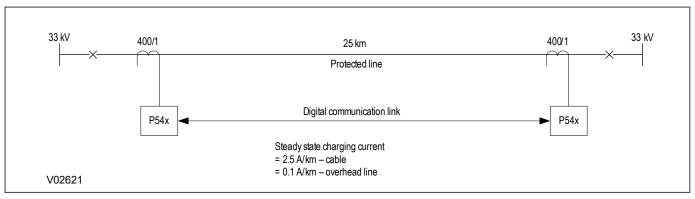

| 6.2                 | Current Differential Protection Principle                                | 93                |

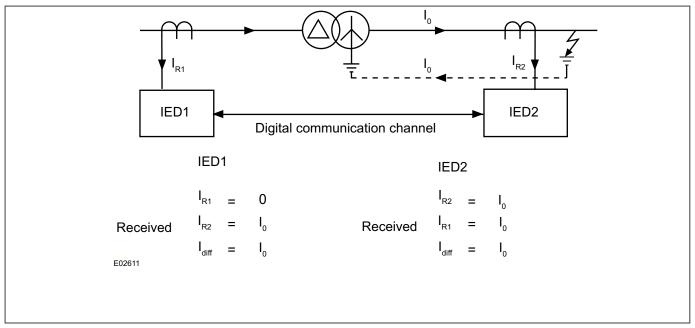

| 6.2.1               | Numerical Current Differential Protection                                | 93                |

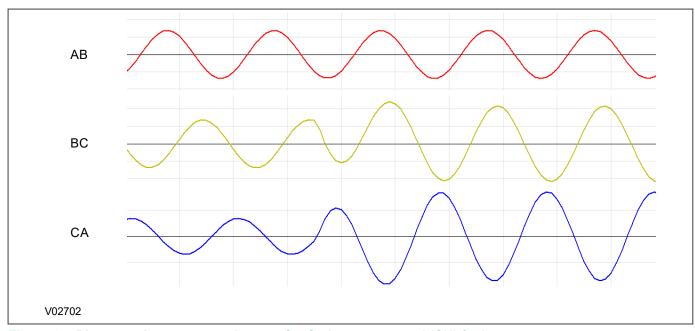

| 6.3                 | Synchronisation of Current Signals                                       | 95                |

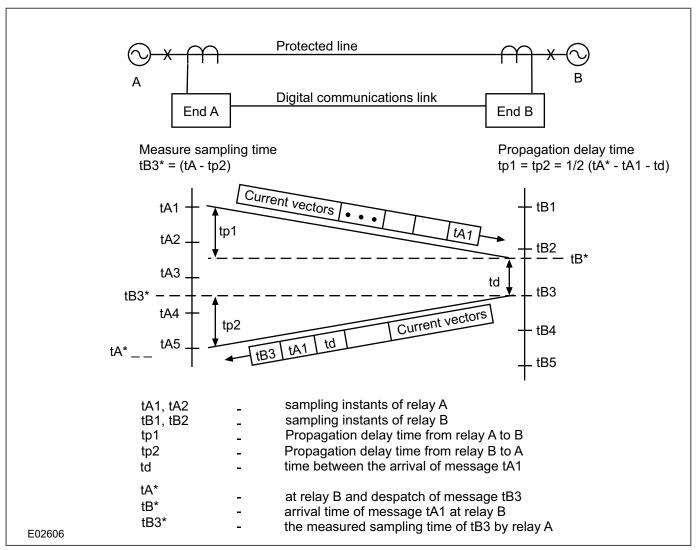

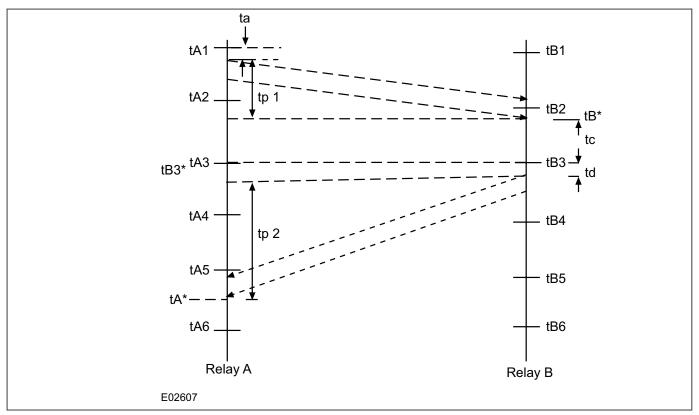

| 6.3.1               | Time Alignment using Ping-Pong Technique                                 | 95                |

| 6.3.2               | GPS Synchronisation                                                      | 96                |

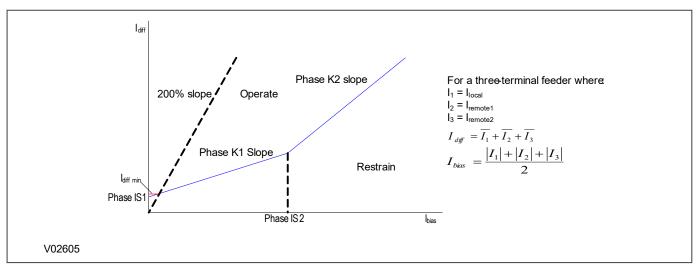

| 6.4                 | Phase Current Differential Protection                                    | 98                |

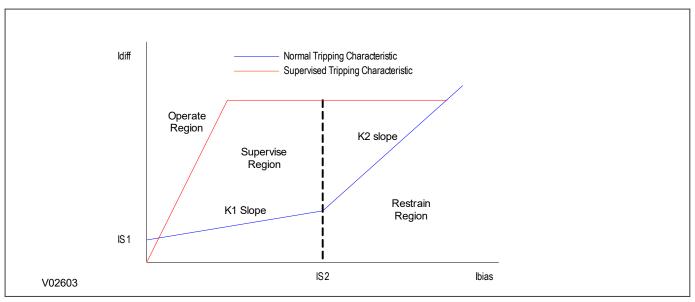

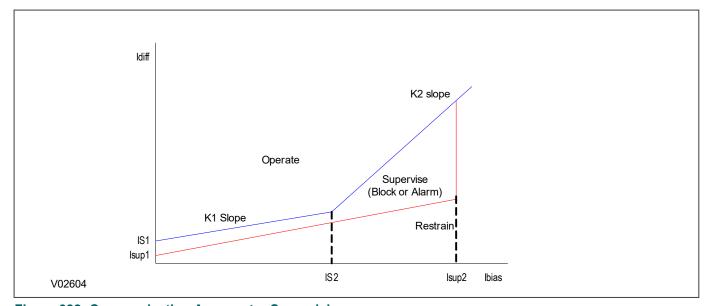

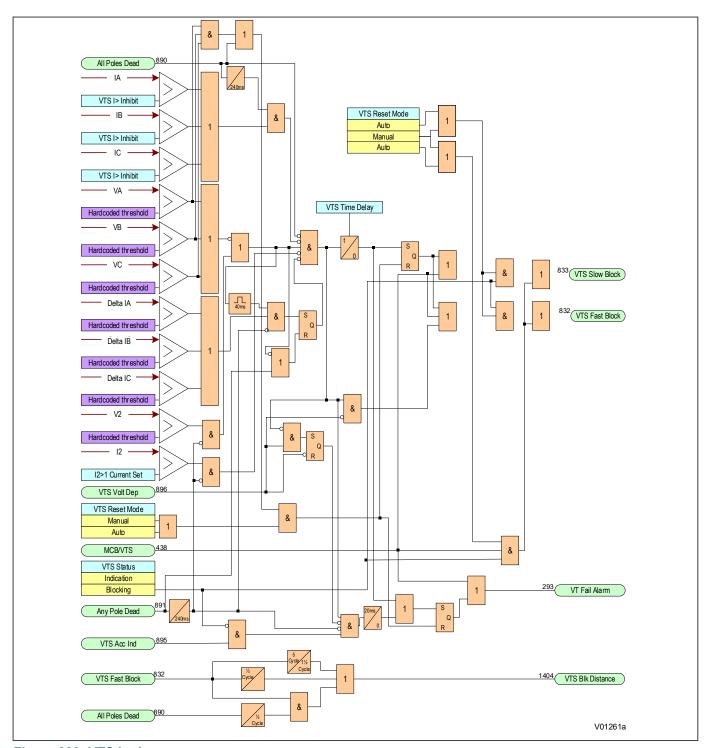

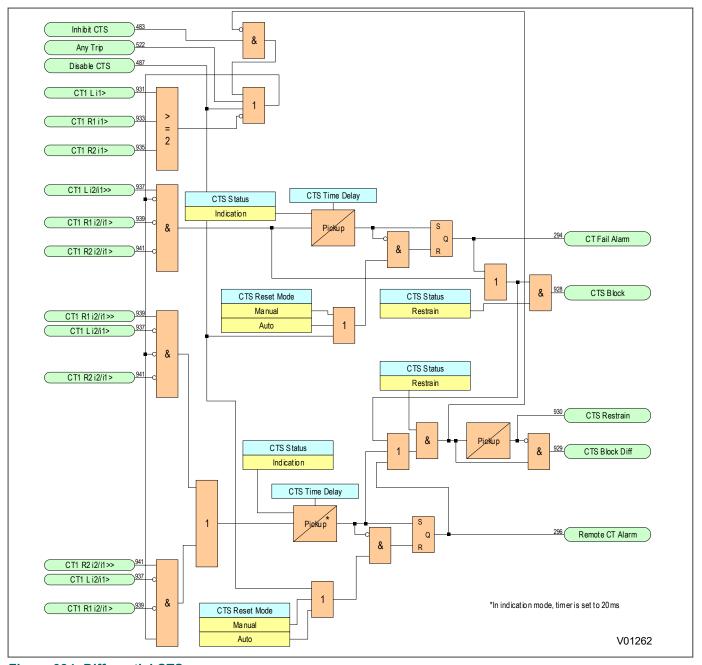

| 6.4.1               | Phase Current Differential Tripping Criteria                             | 99                |

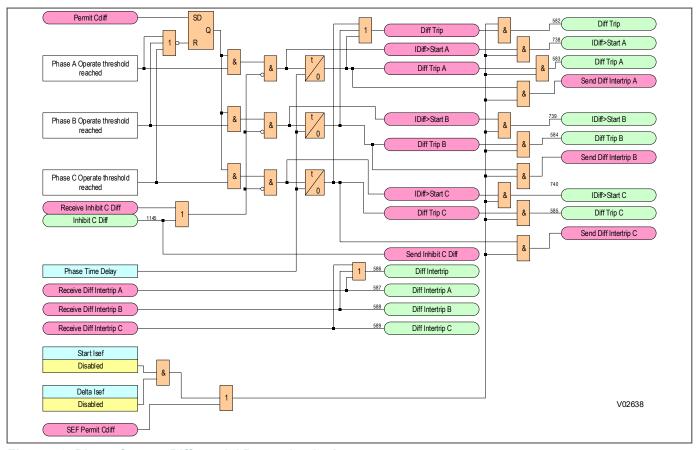

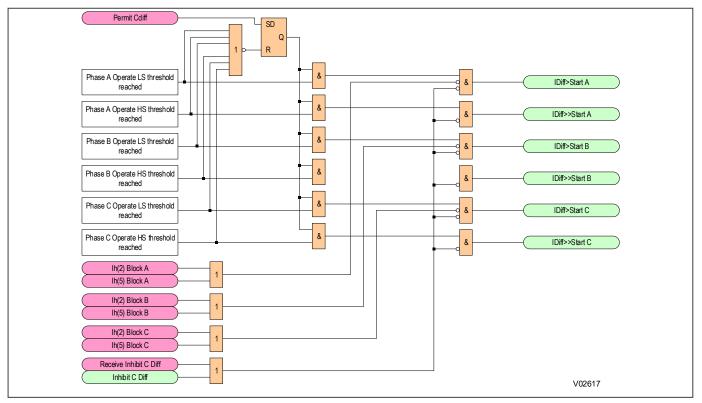

| 6.4.2               | Phase Current Differential Protection Logic                              | 100               |

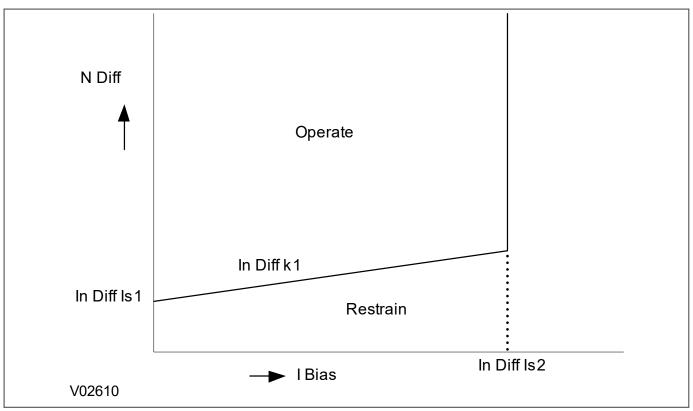

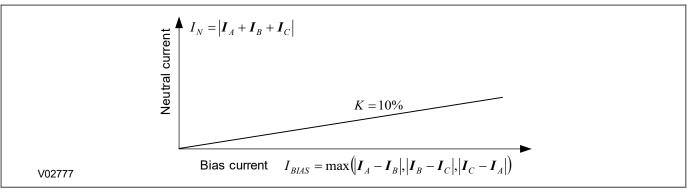

| <b>6.5</b>          | Neutral Current Differential Protection                                  | 101               |

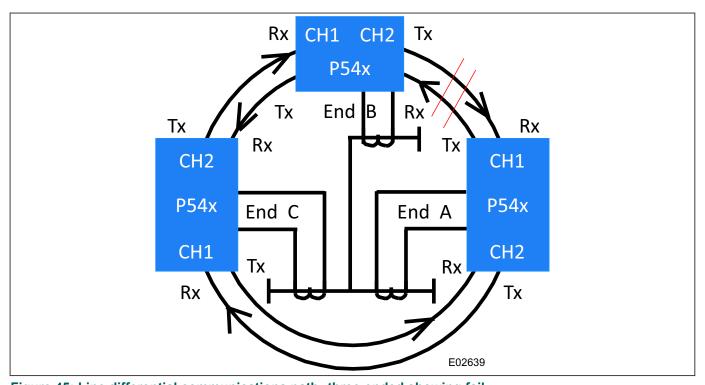

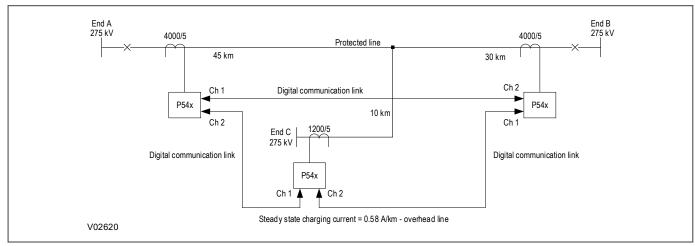

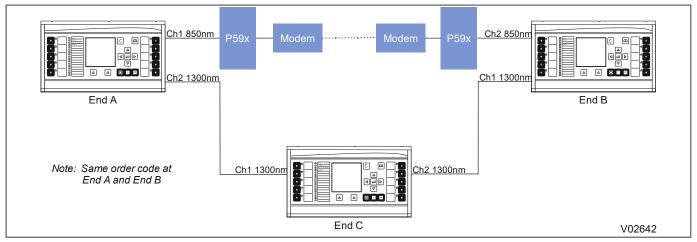

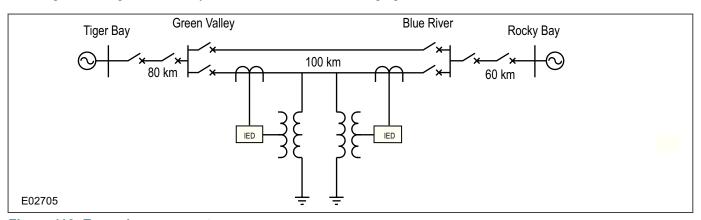

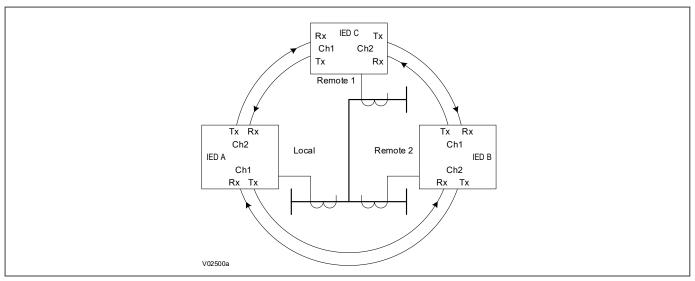

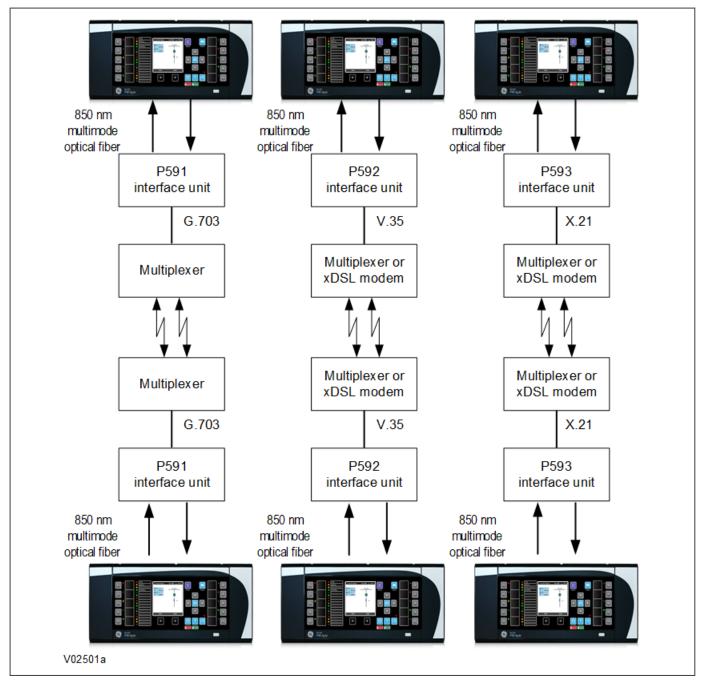

| 6.5.1<br><b>6.6</b> | Neutral Current Differential Characteristic Three-Terminal Schemes       | 101<br><b>103</b> |

| 6.6.1               | Communication Path Failure                                               | 104               |

| 6.6.2               | Three-Terminal Scheme Reconfiguration on Energisation                    | 104               |

| 6.7                 | Transient Bias                                                           | 106               |

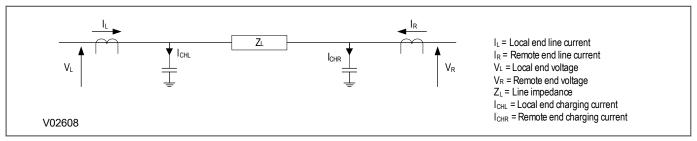

| 6.8                 | Capacitive Charging Current Compensation                                 | 107               |

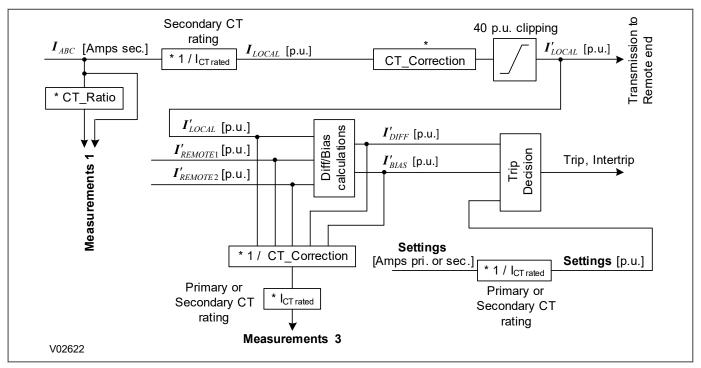

| 6.9                 | CT Compensation                                                          | 108               |

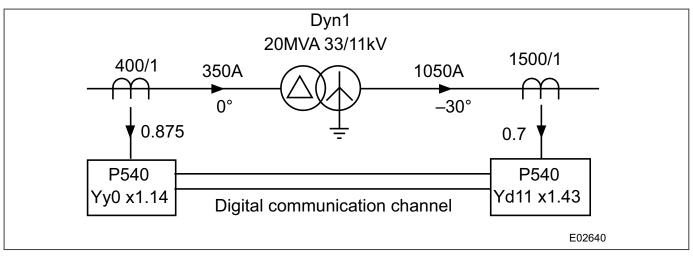

| 6.10                | Feeders with In-Zone Transformers                                        | 109               |

| 6.10.1              | CT Phase Correction                                                      | 109               |

| 6.10.2              | Zero Sequence Filtering                                                  | 110               |

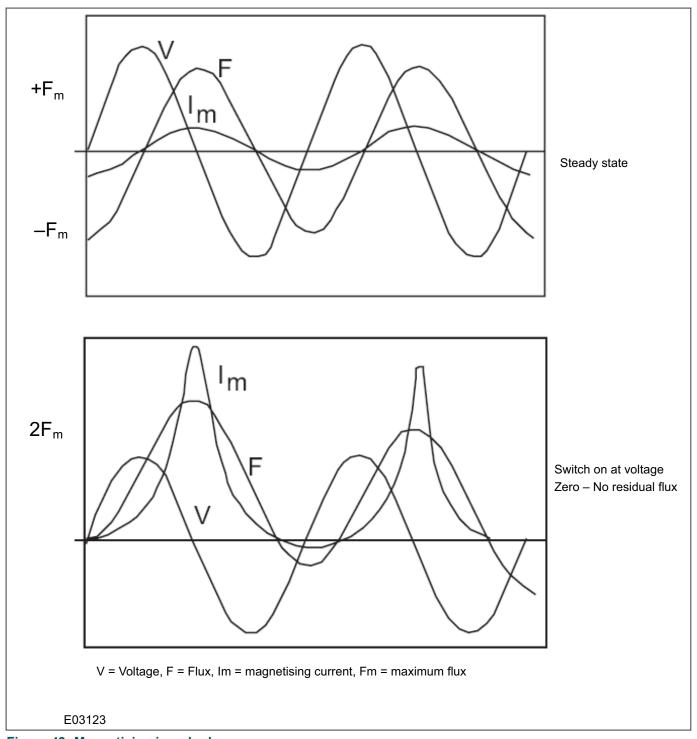

| 6.10.3              | Magnetising Inrush Restraint                                             | 111               |

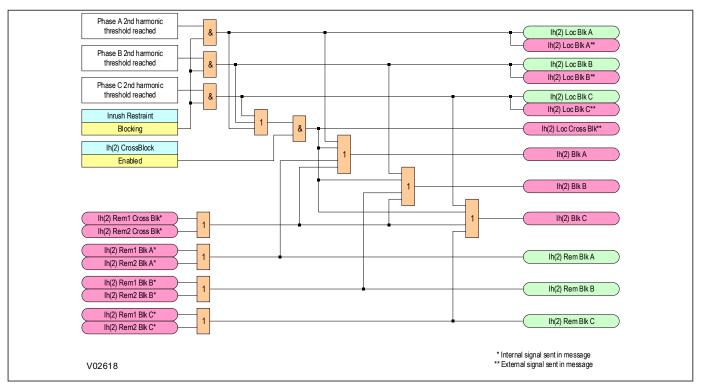

| 6.10.3.1            | Second Harmonic Restraint                                                | 113               |

| 6.10.4              | Overfluxing Restraint                                                    | 114               |

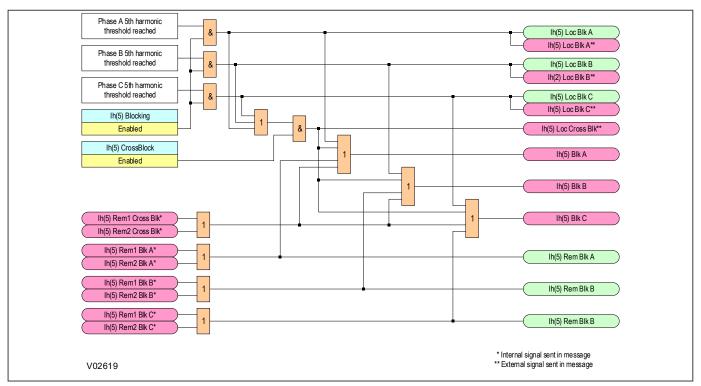

| 6.10.4.1            | Fifth Harmonic Blocking                                                  | 114               |

| 6.11                | Logic for Feeders with In-Zone Transformers                              | 116               |

| 6.12                | Second Harmonic Blocking Logic                                           | 117               |

| 6.13                | Fifth Harmonic Blocking Logic                                            | 118               |

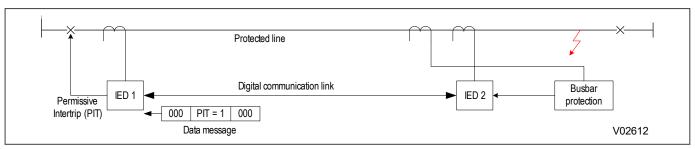

| 6.14                | Current Differential Intertripping                                       | 119               |

P54-TM-EN-2

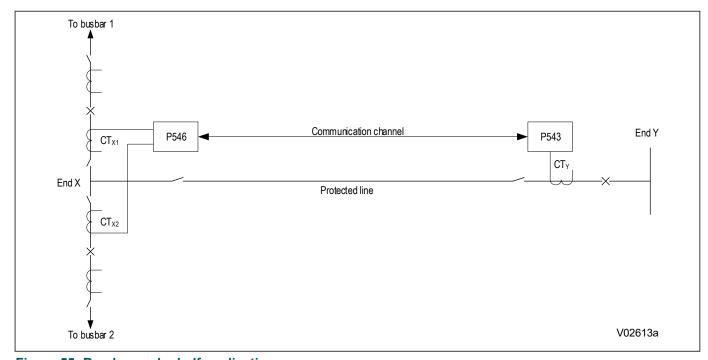

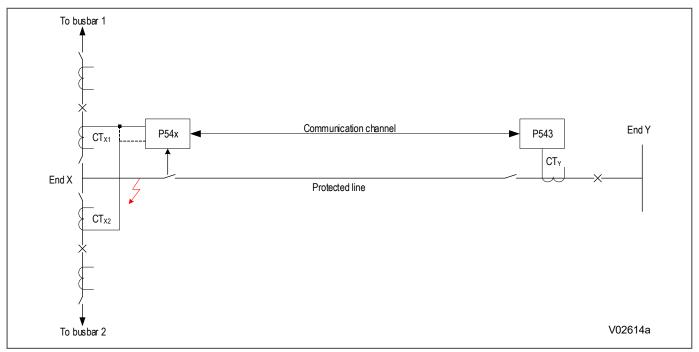

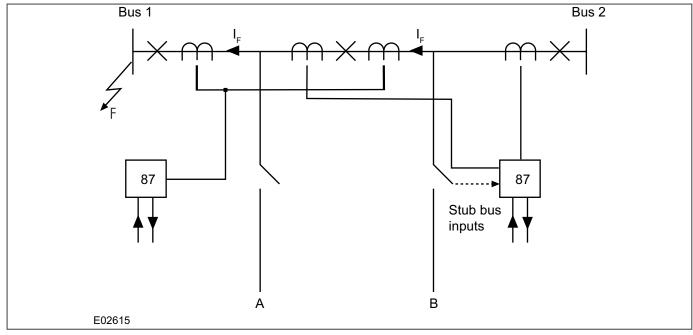

| <b>6.15 6.16 6.17 6.18</b> 6.18.1 | Mesh Corner and Breaker-And-A-Half Schemes Stub Bus Differential Protection Differential IED compatibility with previous versions Application Notes Setting Up the Phase Differential Characteristic | 120<br>122<br>123<br>124<br>124 |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 6.18.2                            | Sensitivity Under Heavy Loads                                                                                                                                                                        | 125                             |

| 6.18.3                            | Permissive Intertripping                                                                                                                                                                             | 126                             |

| 6.18.4                            | CT Ratio Correction Setting Guidelines                                                                                                                                                               | 126                             |

| 6.18.5                            | Feeders with Small Tapped Loads                                                                                                                                                                      | 127                             |

| 6.18.6                            | Setting a Two-Terminal Phase Current Differential Element                                                                                                                                            | 127                             |

| 6.18.7                            | Setting a Three-Terminal Phase Current Differential Element                                                                                                                                          | 128                             |

| 6.18.8                            | Transformer Feeder Application Example                                                                                                                                                               | 130                             |

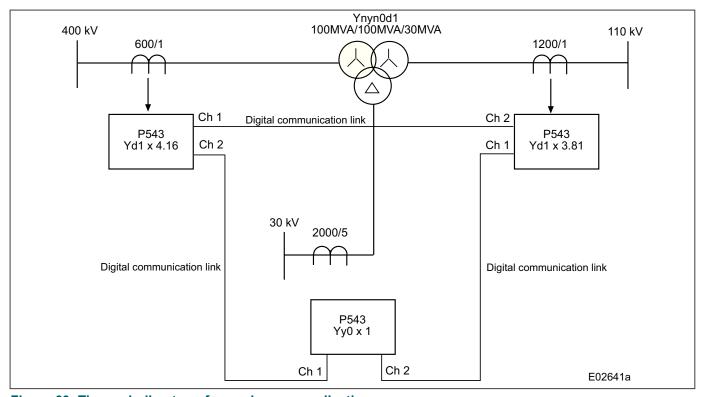

| 6.18.9                            | Three Winding Transformer in Zone Example                                                                                                                                                            | 131                             |

| 6.18.10                           | Mesh Corner and Breaker-and-a-half Application Notes                                                                                                                                                 | 134                             |

| 6.18.11                           | Channel Switch Setting                                                                                                                                                                               | 134                             |

| Chapter                           | r 7 Distance Protection                                                                                                                                                                              | 137                             |

| 7.1                               | Chapter Overview                                                                                                                                                                                     | 138                             |

| <b>7.2</b>                        | Introduction                                                                                                                                                                                         | 139                             |

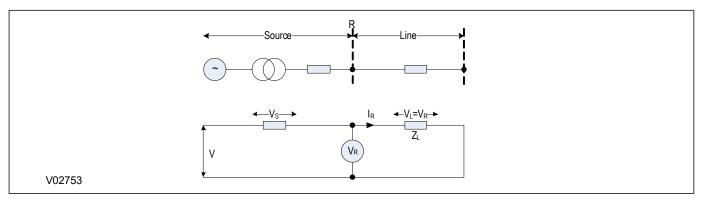

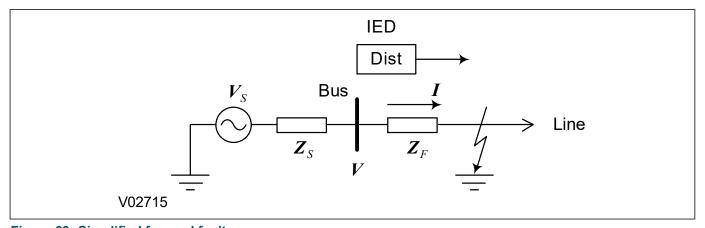

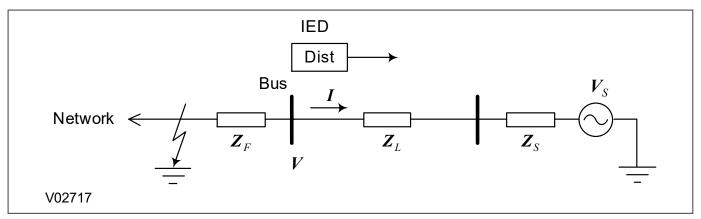

| 7.2.1<br>7.2.2                    | Distance Protection Principle                                                                                                                                                                        | 139<br>139                      |

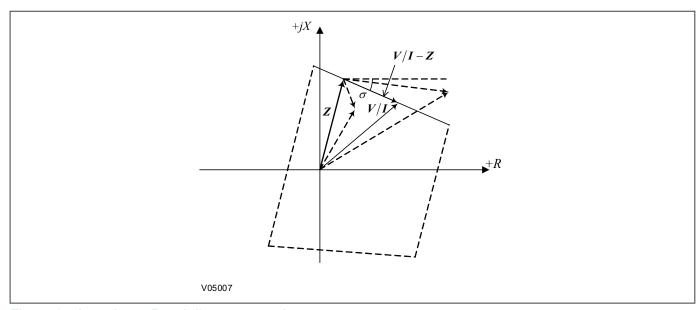

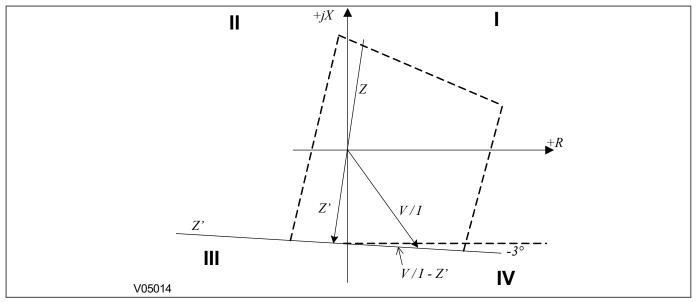

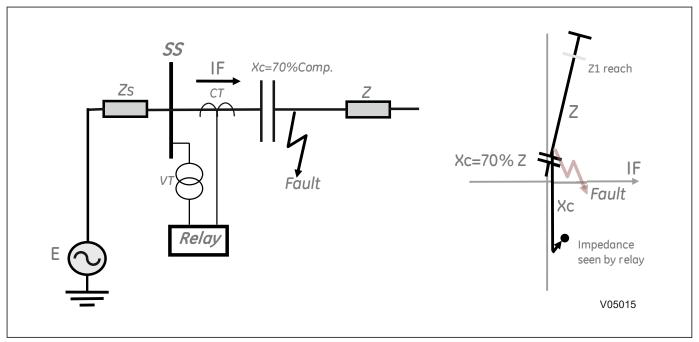

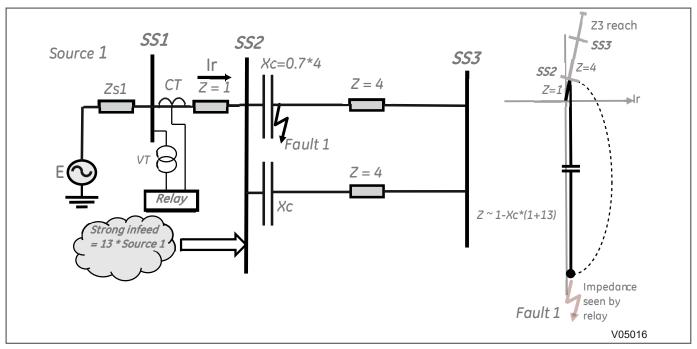

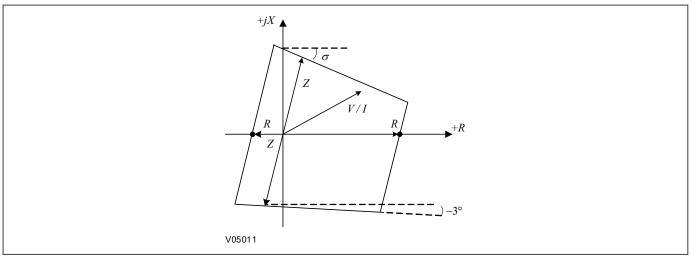

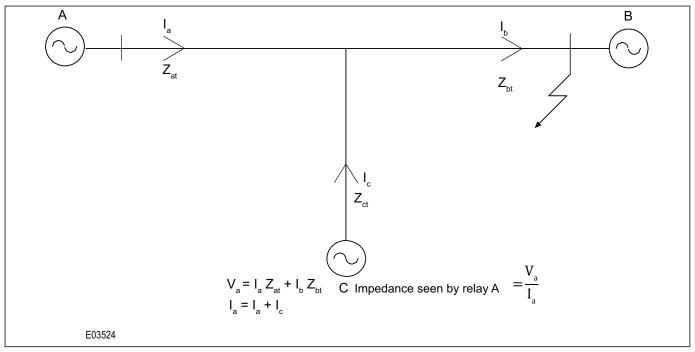

| 7.2.2                             | Performance Influencing Factors Impedance Calculation                                                                                                                                                | 140                             |

| 7.2.3<br>7.2.4                    | Implementation with Comparators                                                                                                                                                                      | 140                             |

| 7.2.5                             | Polarization of Distance Characteristics                                                                                                                                                             | 140                             |

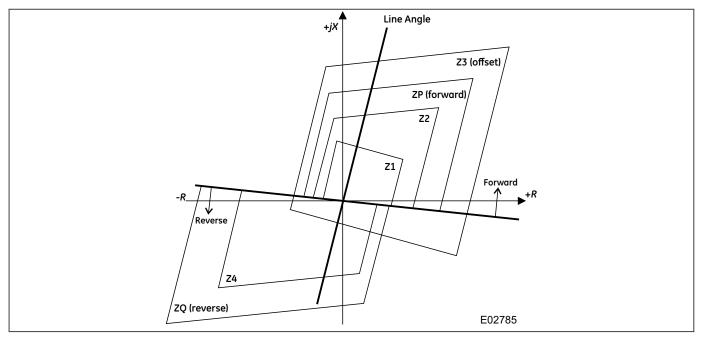

| 7.3                               | Distance Measuring Zones Operating Principles                                                                                                                                                        | 141                             |

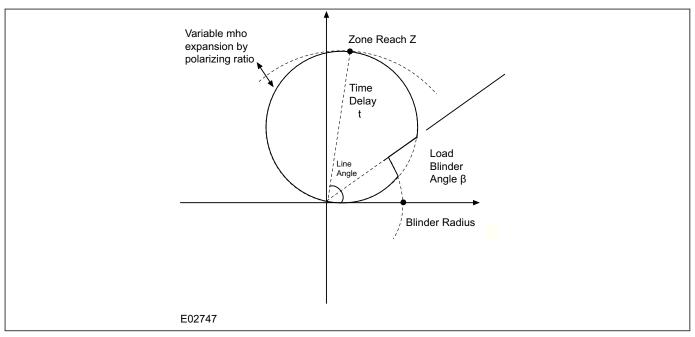

| 7.3.1                             | Mho Characteristics                                                                                                                                                                                  | 142                             |

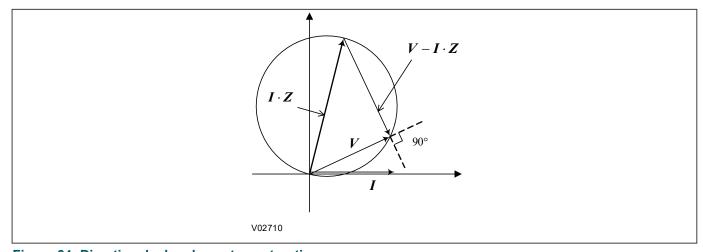

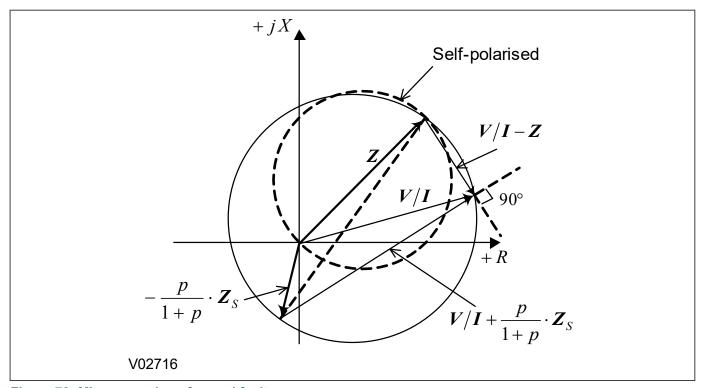

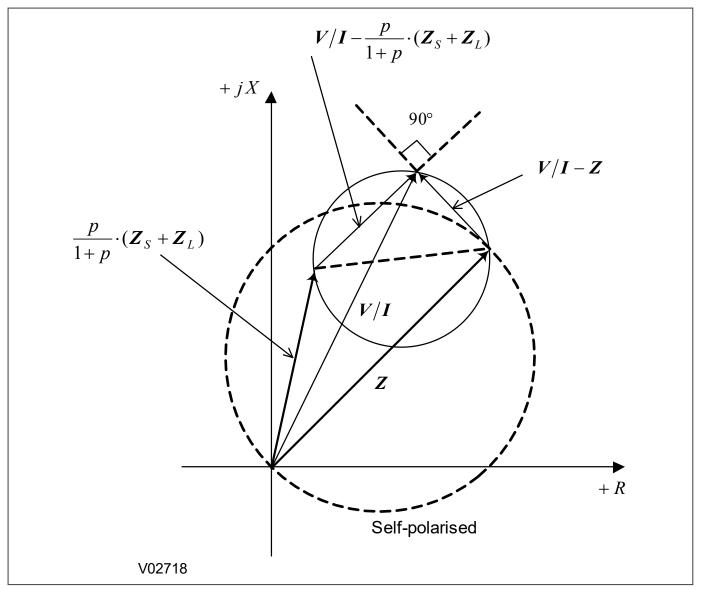

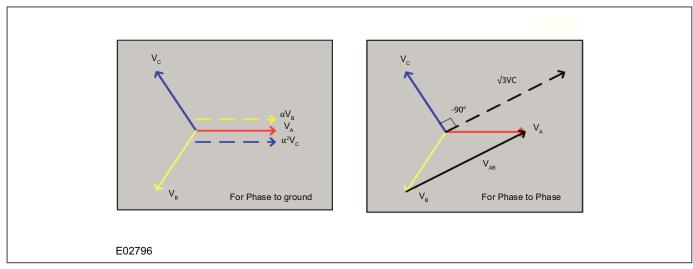

| 7.3.1.1                           | Directional Mho Characteristic for Phase Faults                                                                                                                                                      | 142                             |

| 7.3.1.2                           | Offset Mho Characteristic for Phase Faults                                                                                                                                                           | 142                             |

| 7.3.1.3                           | Directional Self-Polarized Mho Characteristic for Earth Faults                                                                                                                                       | 143                             |

| 7.3.1.4                           | Offset Mho Characteristic for Earth Faults                                                                                                                                                           | 145                             |

| 7.3.1.5                           | Memory Polarization of Mho Characteristics                                                                                                                                                           | 147                             |

| 7.3.1.6                           | Dynamic Mho Expansion and Contraction                                                                                                                                                                | 147                             |

| 7.3.1.7<br>7.3.1.8                | Cross Polarization of Mho Characteristics Implementation of Mho Polarization                                                                                                                         | 150<br>151                      |

| 7.3.1.0<br><b>7.4</b>             | Quadrilateral Characteristic                                                                                                                                                                         | 153                             |

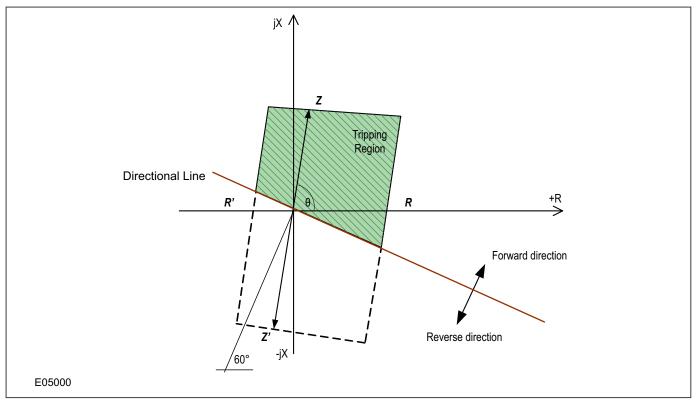

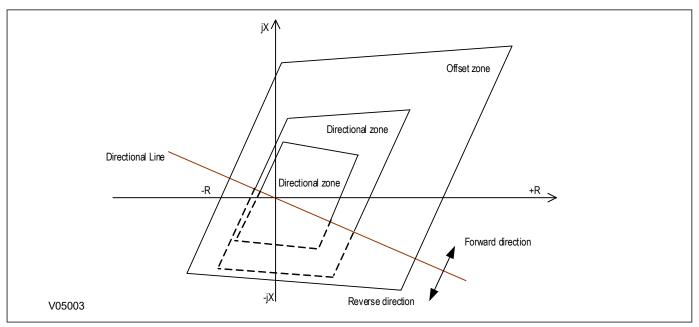

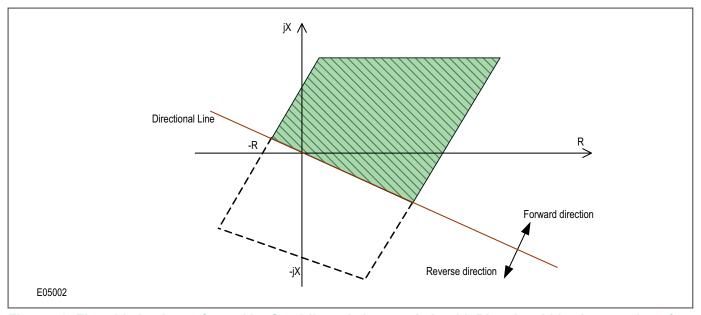

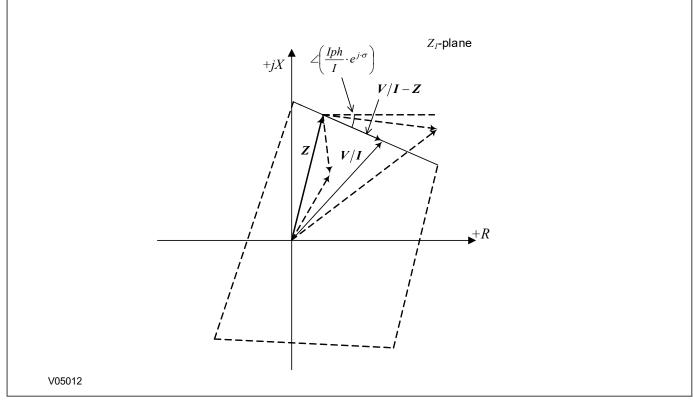

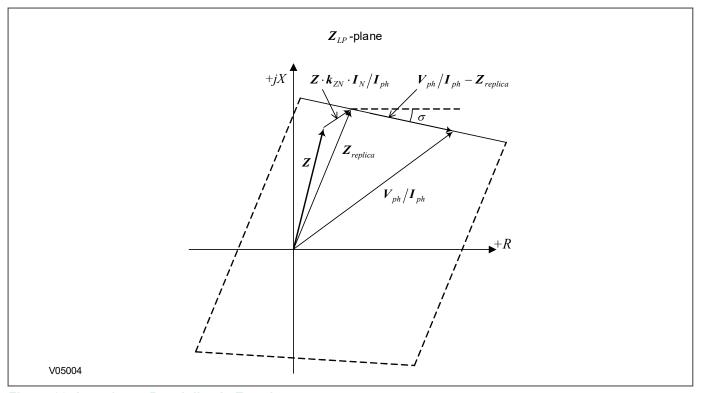

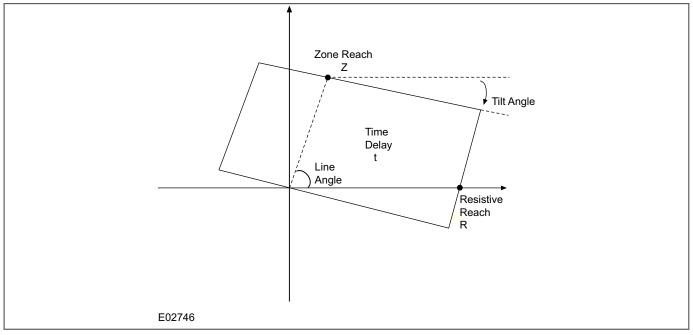

| 7.4.1                             | Directional Quadrilaterals                                                                                                                                                                           | 154                             |

| 7.5                               | Earth Fault Quadrilateral Characteristics                                                                                                                                                            | 160                             |

| 7.5.1                             | Earth Fault Reactance Lines                                                                                                                                                                          | 160                             |

| 7.5.2                             | Earth Fault Fixed Reactance Line Tilting                                                                                                                                                             | 161                             |

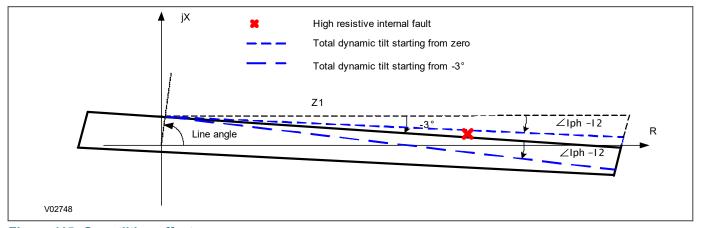

| 7.5.3                             | Earth Fault Dynamic Reactance Line Tilting                                                                                                                                                           | 163                             |

| 7.5.4                             | Earth Fault Resistive Blinders                                                                                                                                                                       | 165                             |

| 7.5.5                             | Earth Fault Quadrilateral Characteristics Summary                                                                                                                                                    | 167                             |

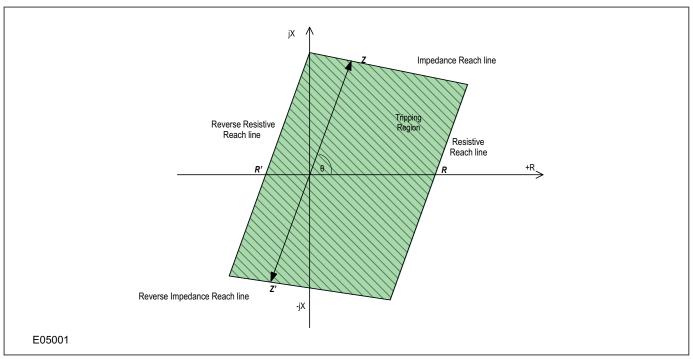

| 7.6                               | Quadrilateral Characteristic for Phase Faults                                                                                                                                                        | 169                             |

| 7.6.1                             | Phase Fault Impedance Reach Line                                                                                                                                                                     | 169                             |

| 7.6.2                             | Reverse Impedance Reach Line                                                                                                                                                                         | 170                             |

| 7.6.3                             | Phase Fault Resistive Reach Line                                                                                                                                                                     | 173                             |

| 7.6.4                             | Phase Fault Reverse Resistive Reach Line                                                                                                                                                             | 174                             |

| 7.6.5                             | Phase Fault Quadrilateral Characteristic Summary                                                                                                                                                     | 174                             |

| <b>7.7</b><br>7.7.1               | Phase and Earth Fault Distance Protection Implementation Phase Fault Characteristics                                                                                                                 | <b>177</b><br>177               |

| 7.7.1<br>7.7.2                    | Earth Fault Characteristics                                                                                                                                                                          | 177<br>177                      |

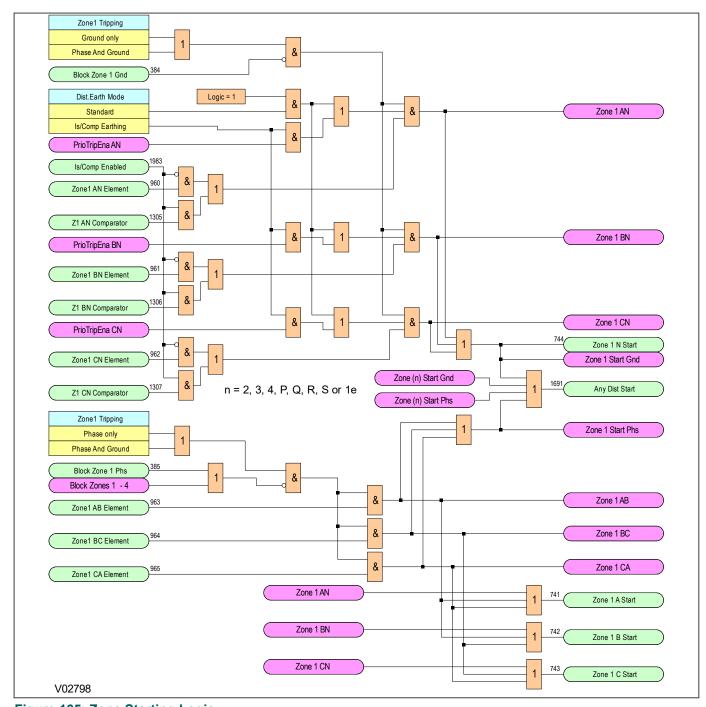

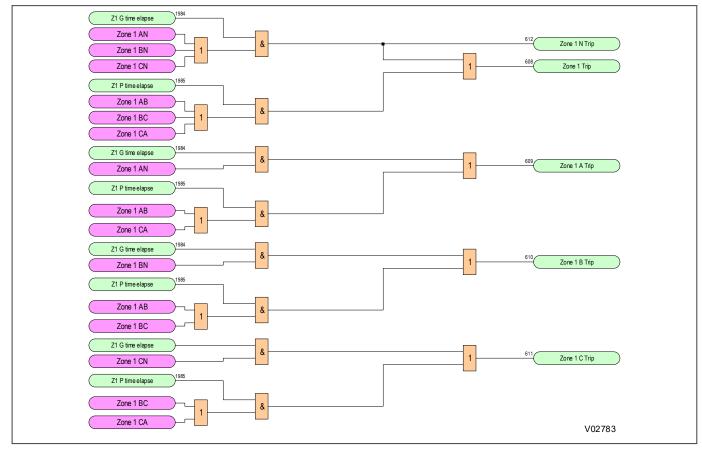

| 7.7.2                             | Distance Protection Tripping Decision                                                                                                                                                                | 177                             |

| 7.7.3<br>7.7.4                    | Distance Protection Phase Selection                                                                                                                                                                  | 178                             |

| 7.7. <del>4</del><br>7.7.4.1      | Faulted Phase Selection                                                                                                                                                                              | 178                             |

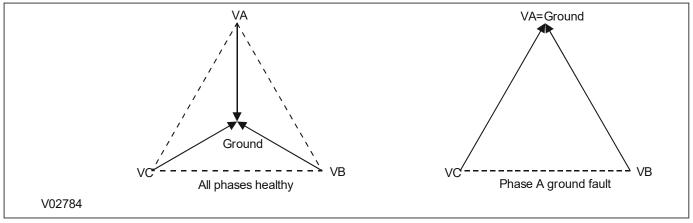

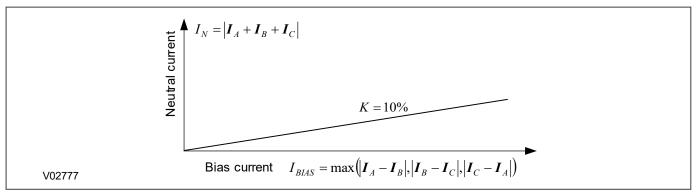

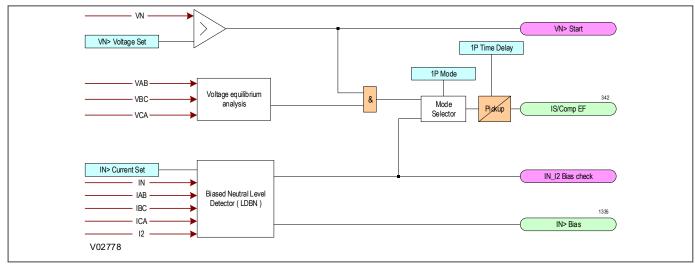

| 7.7.5                             | Biased Neutral Current Detector and Fault-Type Supervision                                                                                                                                           | 179                             |

| 7.7.6                             | Directionalizing the Distance Elements                                                                                                                                                               | 180                             |

iv P54-TM-EN-2

| 8.1      | Chapter Overview                                                            | 218        |

|----------|-----------------------------------------------------------------------------|------------|

| Chapter  |                                                                             | 217        |

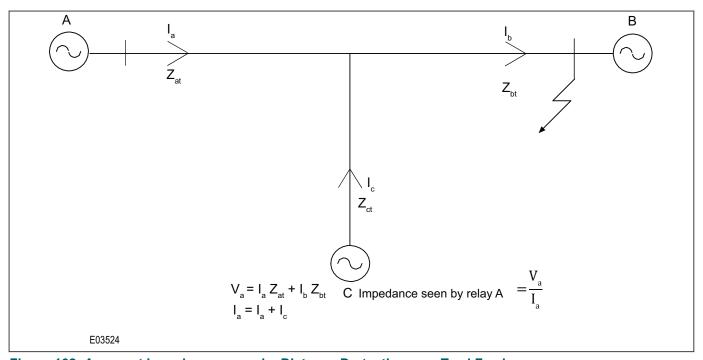

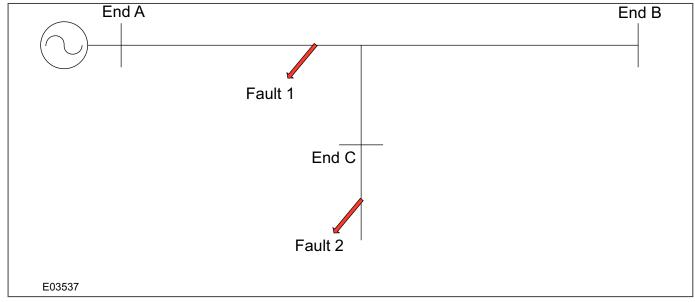

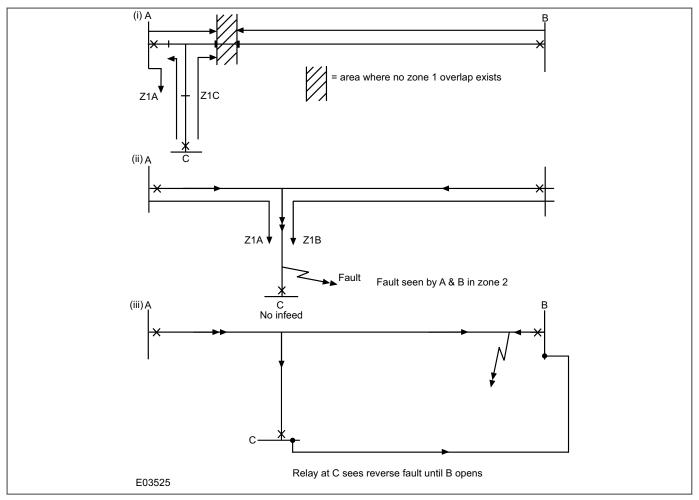

| 7.9.12   | Teed Feeder Applications                                                    | 216        |

| 7.9.11.9 | Quadrilateral Resistive Reach Settings                                      | 214        |

| 7.9.11.8 | Load Avoidance                                                              | 214        |

| 7.9.11.7 | Zone 4 Reverse Reach Settings                                               | 213        |

| 7.9.11.6 | Zone 3 Reverse Reach Settings                                               | 213        |

| 7.9.11.5 | Zone 3 Phase and Ground Reach Settings                                      | 213        |

| 7.9.11.4 | Zone 2 Phase and Ground Reach Settings                                      | 213        |

| 7.9.11.3 | Zone 1 Phase and Ground Reach Settings                                      | 212        |

| 7.9.11.2 | Residual Compensation for Earth Fault Elements                              | 212        |

| 7.9.11.1 | Line Impedance Calculation                                                  | 212        |

| 7.9.11   | Distance Protection Worked Example                                          | 211        |

| 7.9.10   | Polarizing Setup                                                            | 210        |

| 7.9.9    | Load Blinding Setup                                                         | 210        |

| 7.9.8.2  | Setting up CVTs                                                             | 209        |

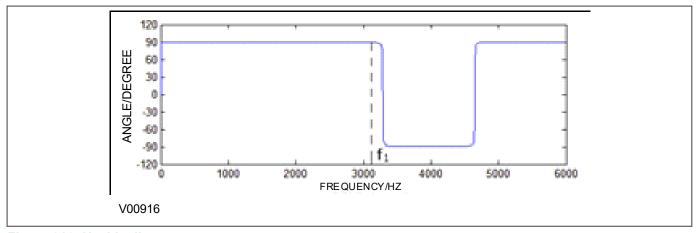

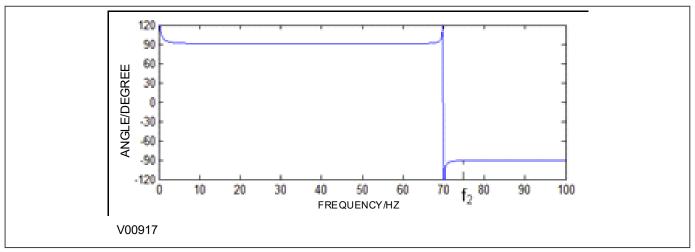

| 7.9.8.1  | Distance Digital Filter                                                     | 209        |

| 7.9.8    | Filtering Setup                                                             | 209        |

| 7.9.7.1  | Delta Thresholds                                                            | 208        |

| 7.9.7    | Delta Directional Element Setting Guidelines                                | 208        |

| 7.9.6    | Directional Element for Distance Protection                                 | 208        |

| 7.9.5    | Phase Fault Zone Settings                                                   | 207        |

| 7.9.4.2  | Fixed Tilting                                                               | 207        |

| 7.9.4.1  | Dynamic Tilting                                                             | 206        |

| 7.9.4    | Earth Fault Resistive Reaches and Tilting                                   | 205        |

| 7.9.3.1  | Quadrilateral Resistive Reaches                                             | 205        |

| 7.9.3    | Zone Reach Setting Guidelines                                               | 204        |

| 7.9.2.2  | Earth Fault Characteristic                                                  | 204        |

| 7.9.2.1  | Phase Characteristic                                                        | 203        |

| 7.9.2    | Operating Characteristic Selection                                          | 203        |

| 7.9.1    | Setting Mode Choice                                                         | 203        |

| 7.9      | Application Notes                                                           | 203        |

| 7.8.3.4  | Phase Preferential Logic                                                    | 197        |

| 7.8.3.3  | Fault Detection Logic                                                       | 196<br>107 |

| 7.8.3.2  | First Earth Fault Detection                                                 | 194        |

| 7.8.3.1  | Network Earthing System Setting                                             | 194        |

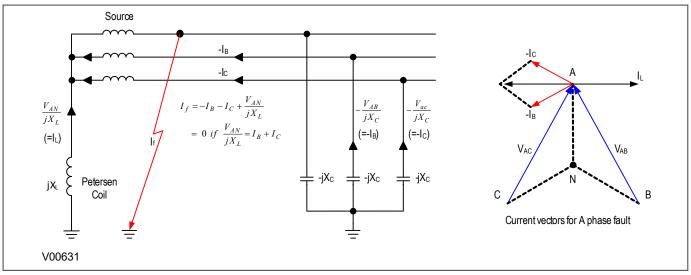

| 7.8.3    | Implementation of Distance Protection for Isolated and Compensated Networks | 194        |

| 7.8.2.2  | Cross-Country Faults on Isolated or Compensated Systems                     | 193        |

| 7.8.2.1  | Single-phase to Earth Faults on Isolated or Compensated Systems             | 193        |

| 7.8.2    | Earth Fault Distance Protection for Isolated and Compensated Systems        | 192        |

| 7.8.1    | Petersen Coil Earthed Systems                                               | 189        |

| 7.8      | Distance Isolated and Compensated Systems                                   | 189        |

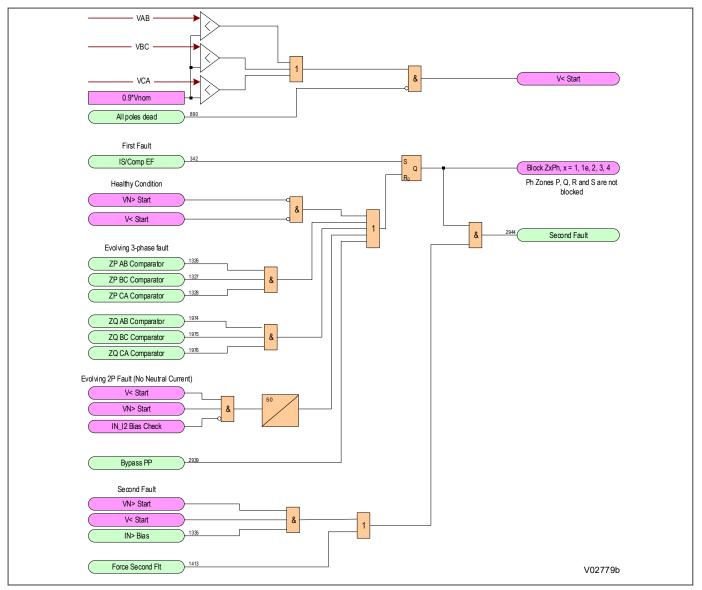

| 7.7.11   | Cross Country Fault Protection                                              | 187        |

| 7.7.10   | Load Blinding                                                               | 186        |

| 7.7.9.2  | CVTs with Active Suppression of Ferroresonance                              | 186        |

| 7.7.9.1  | CVTs with Passive Suppression of Ferroresonance                             | 186        |

| 7.7.9    | Capacitor VT Applications                                                   | 185        |

| 7.7.8.2  | Distance Zone Sensitivities                                                 | 185        |

| 7.7.8.1  | Advanced Distance Zone Settings                                             | 184        |

| 7.7.8    | Distance Element Zone Settings                                              | 184        |

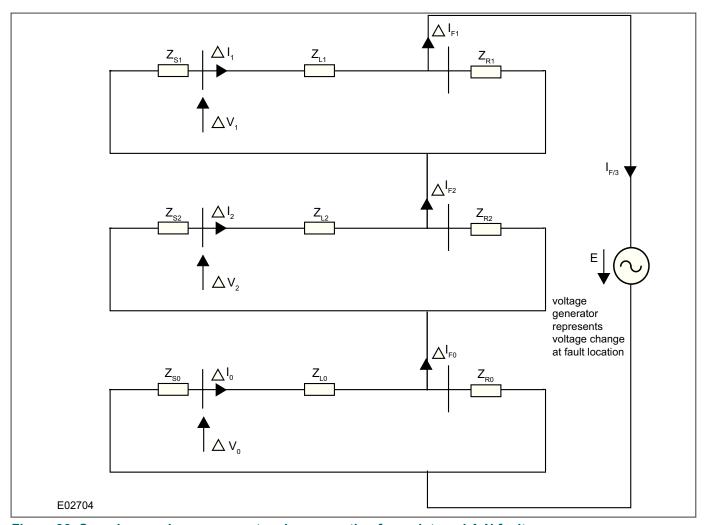

| 7.7.7.2  | Delta Directional Decision                                                  | 182        |

| 7.7.7.1  | Delta Directional Principle and Setup                                       | 181        |

| 7.7.7    | Delta Directional Element                                                   | 180        |

P54-TM-EN-2

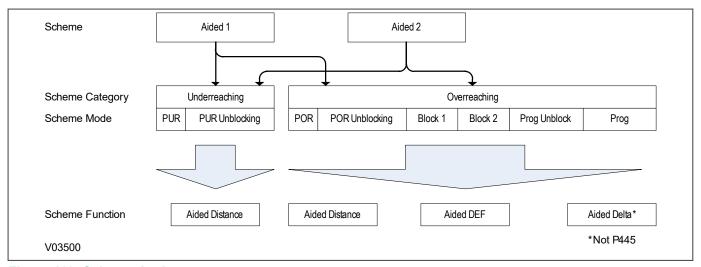

| 8.3.1.1           | Carrier Aided Scheme Types                | 220 |

|-------------------|-------------------------------------------|-----|

| 8.3.1.2           | Default Carrier Aided Schemes             | 221 |

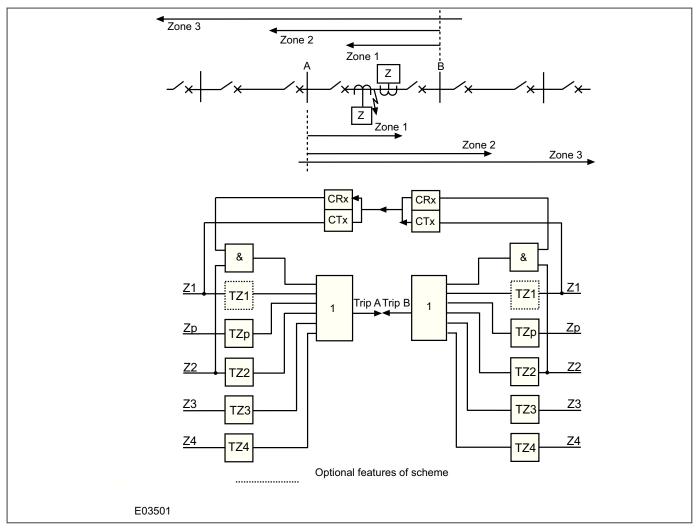

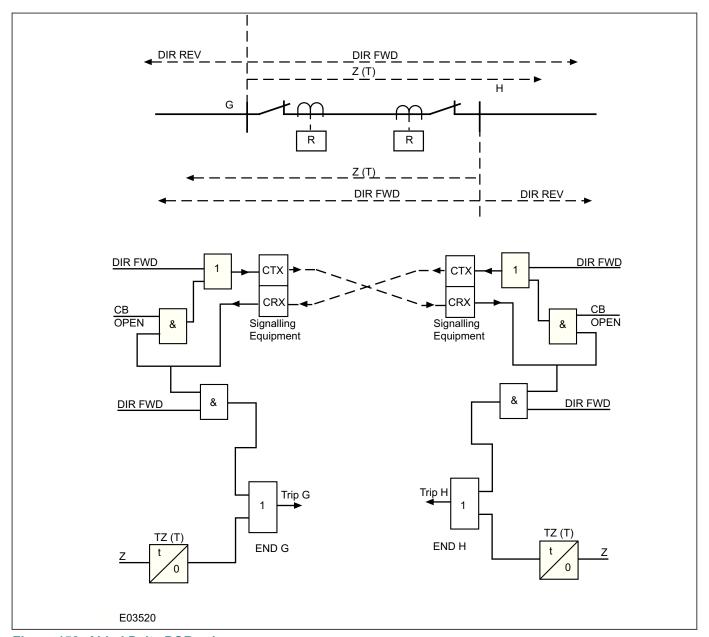

| 8.3.2             | Permissive Underreach Scheme              | 222 |

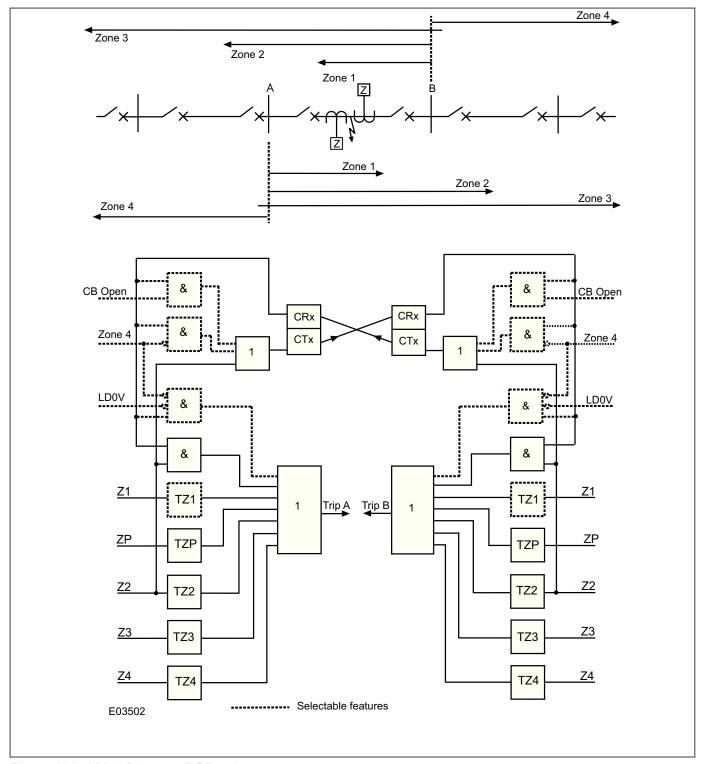

| 8.3.3             | Permissive Over-reach Scheme              | 223 |

| 8.3.3.1           | Permissive Overreach Trip Reinforcement   | 225 |

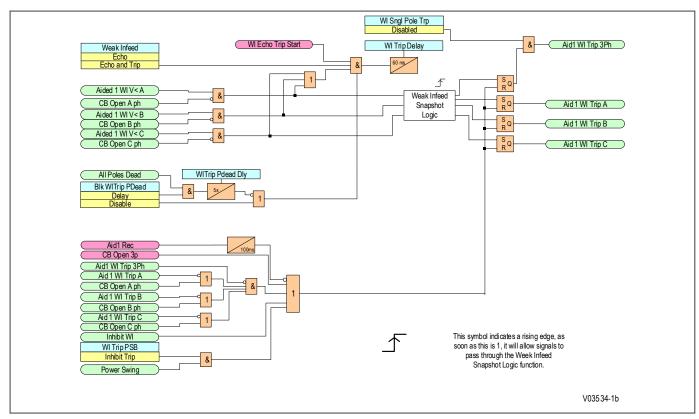

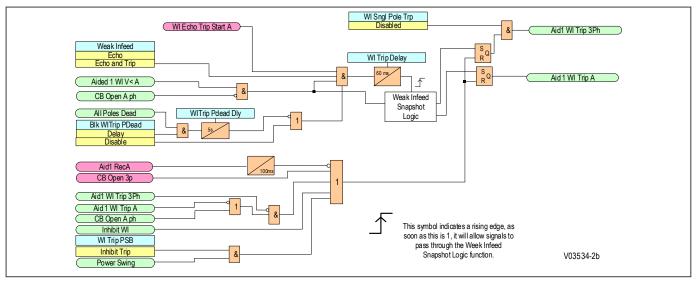

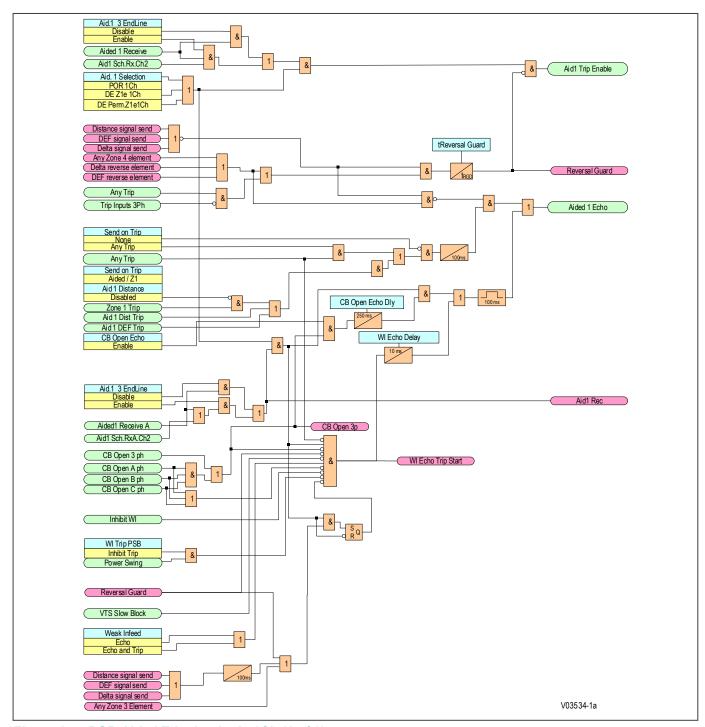

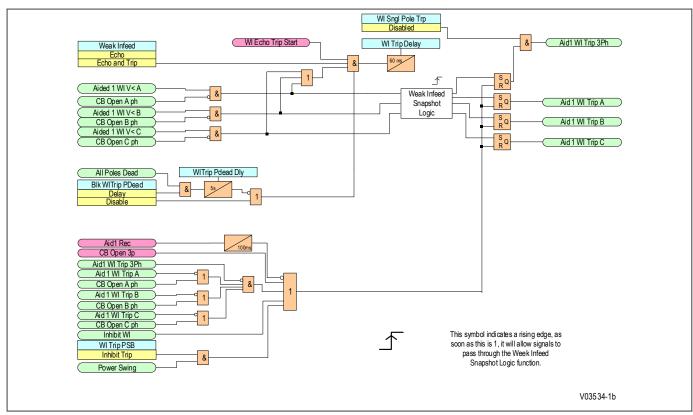

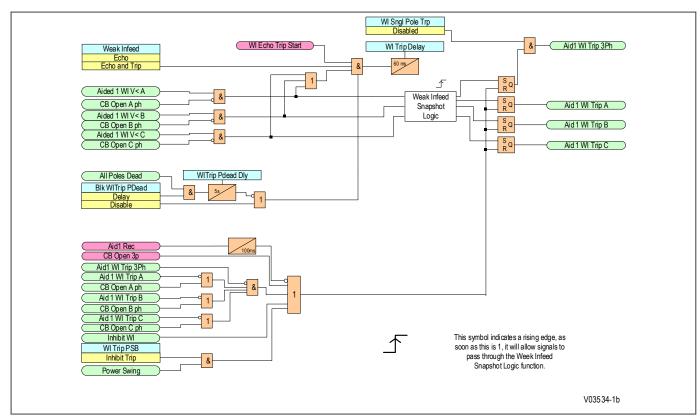

| 8.3.3.2           | Permissive Overreach Weak Infeed Features | 226 |

| 8.3.4             | Permissive Scheme Loss Of Guard           | 226 |

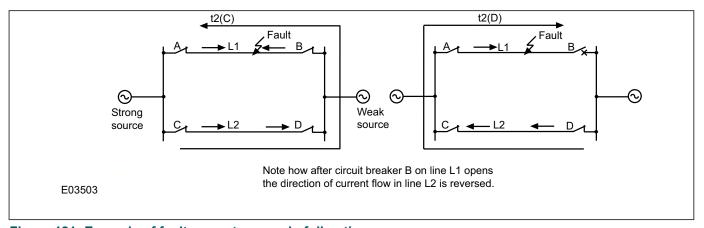

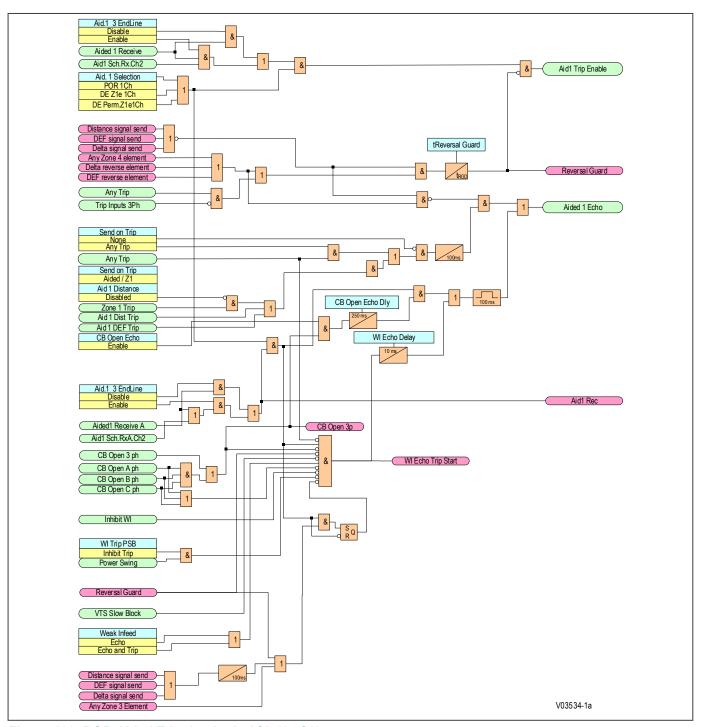

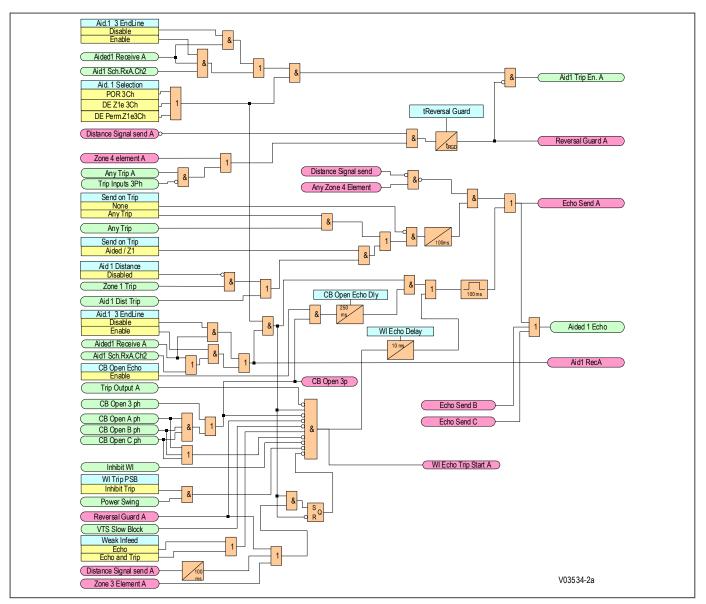

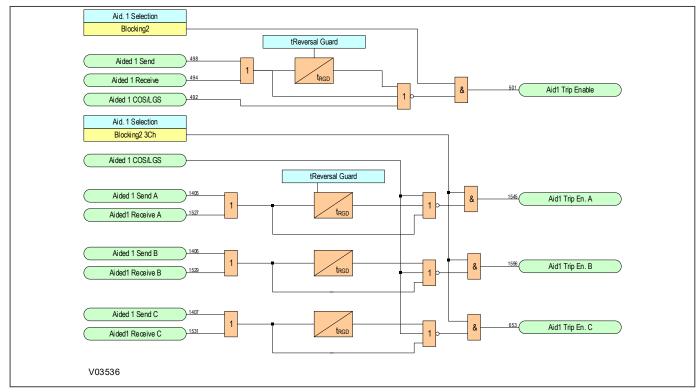

| 8.3.5             | Current Reversal Guard Logic              | 227 |

| 8.3.6             | Aided Distance Blocking Schemes           | 228 |

| 8.3.7             | Aided Distance Unblocking Schemes         | 229 |

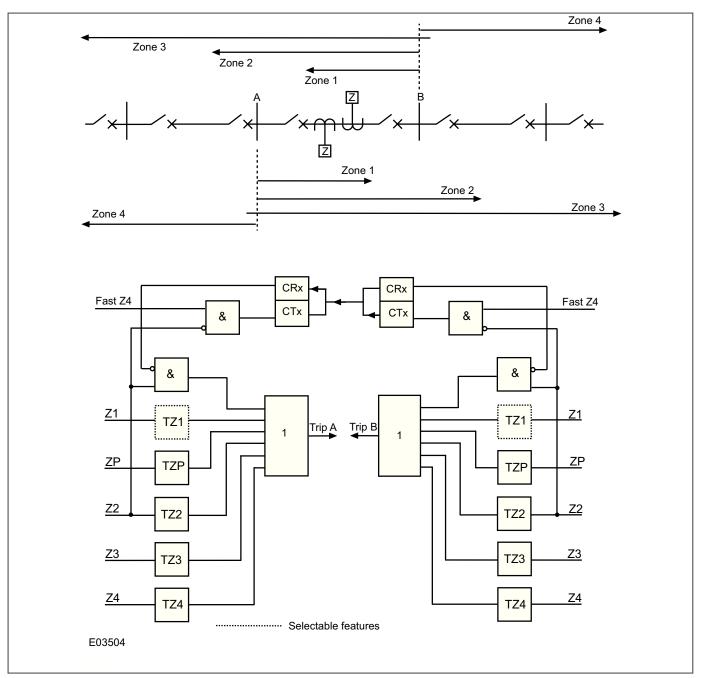

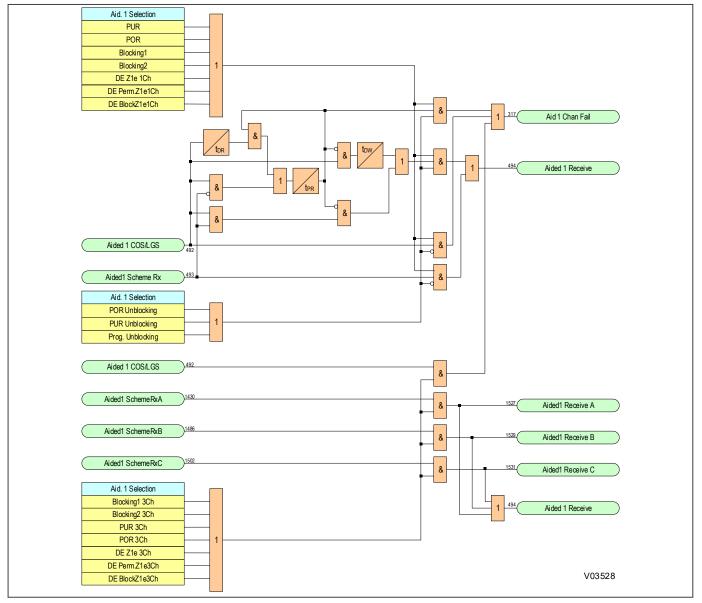

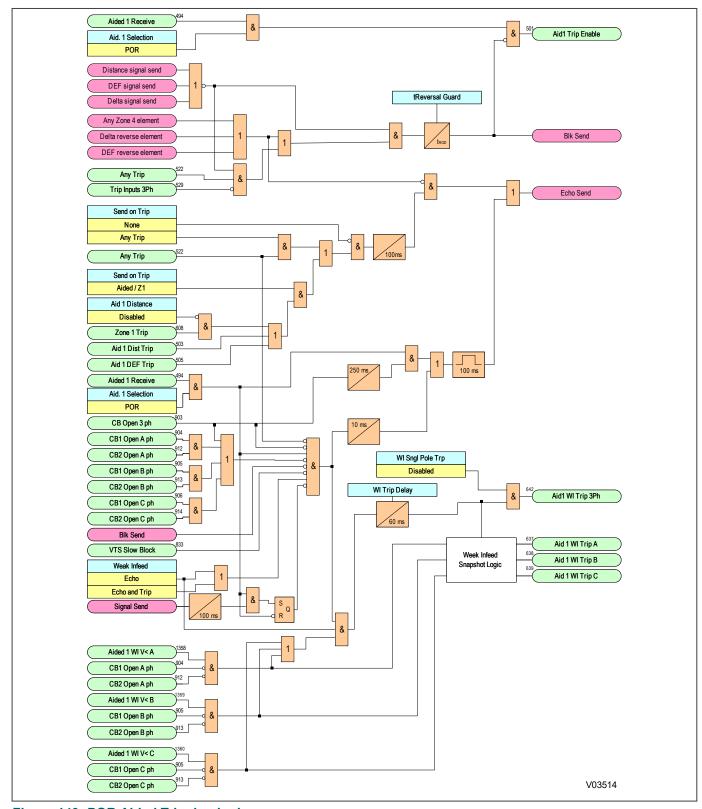

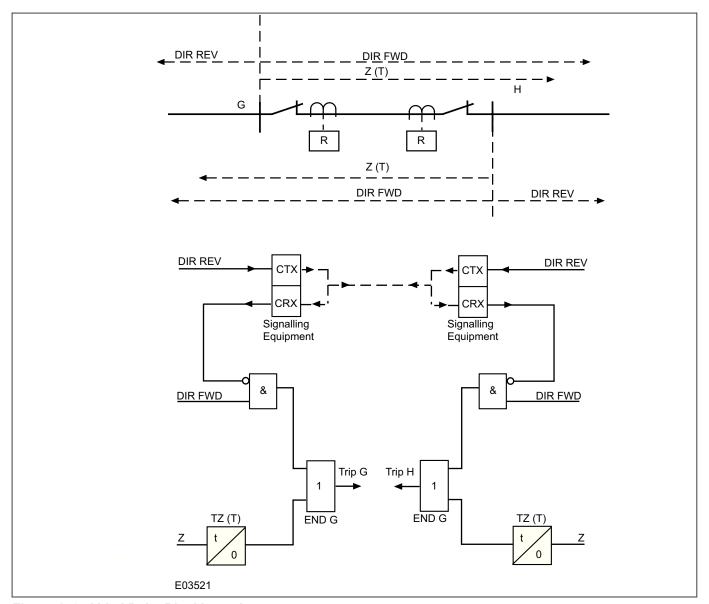

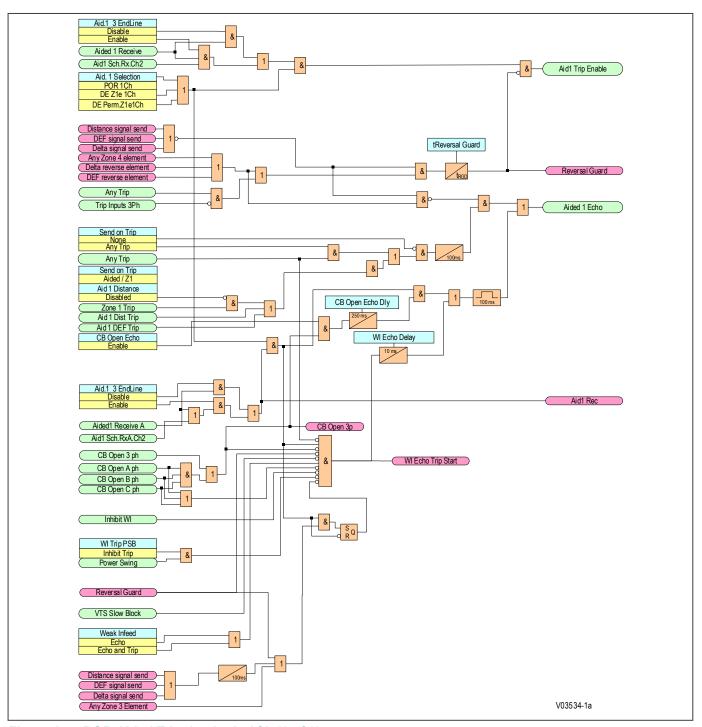

| 8.3.8             | Aided Distance Logic Diagrams             | 231 |

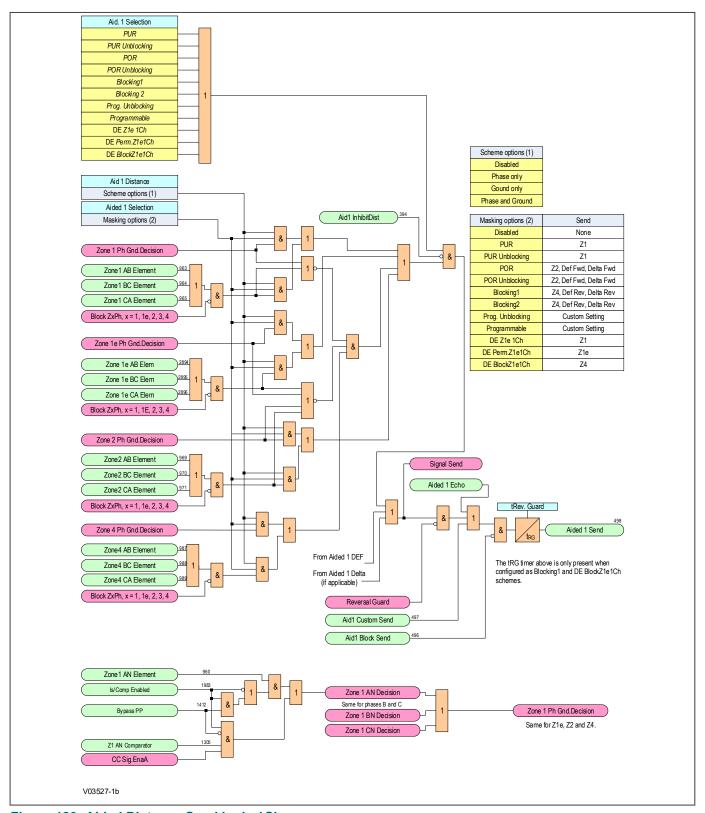

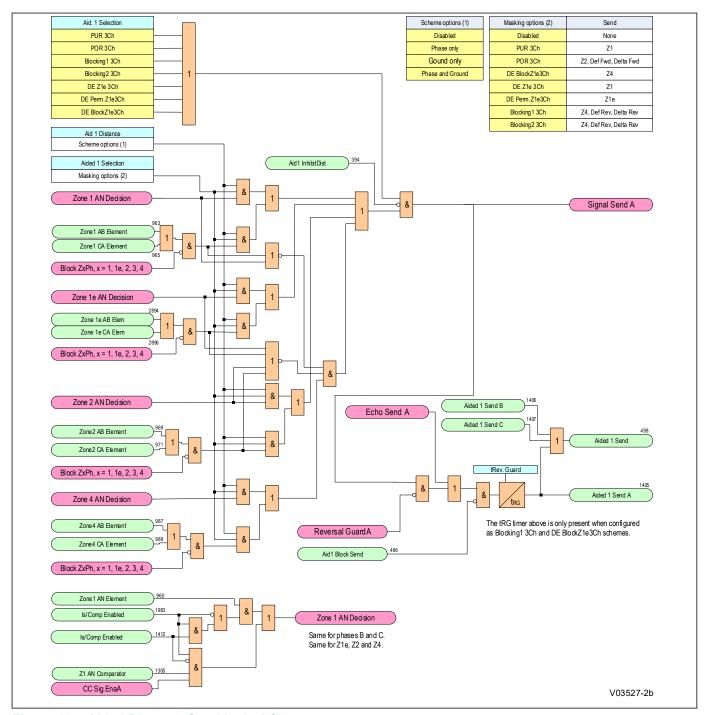

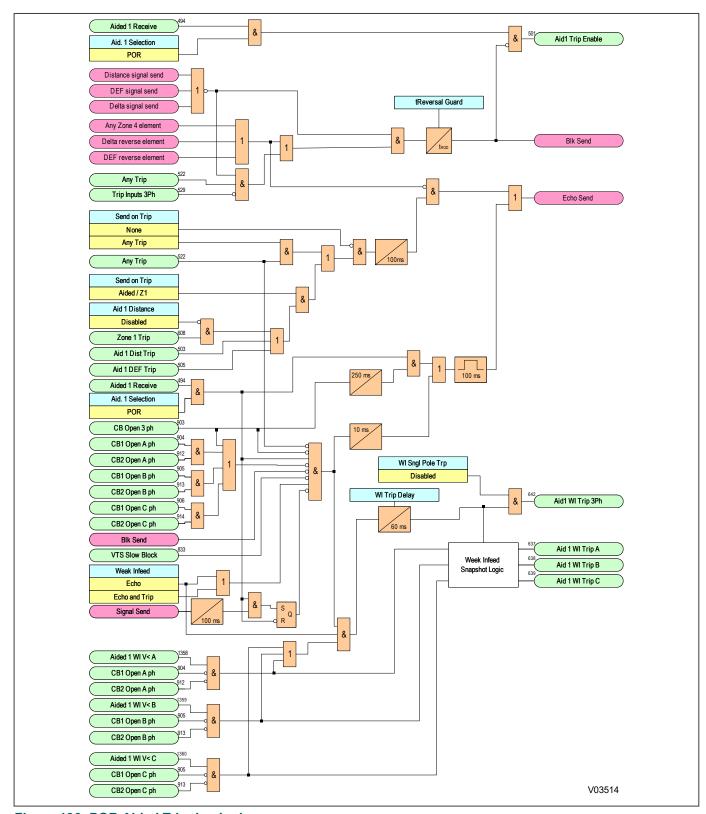

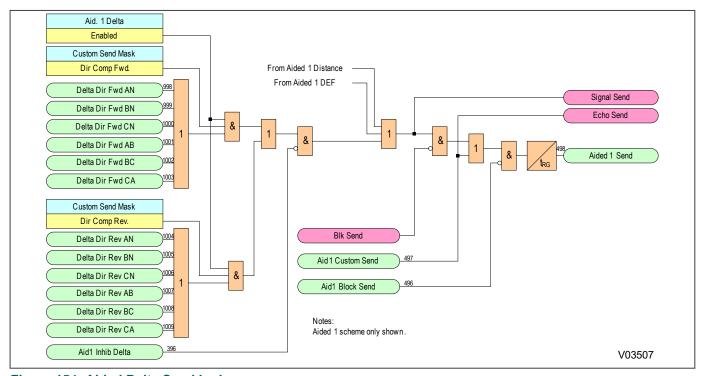

| 8.3.8.1           | Aided Distance Send Logic                 | 231 |

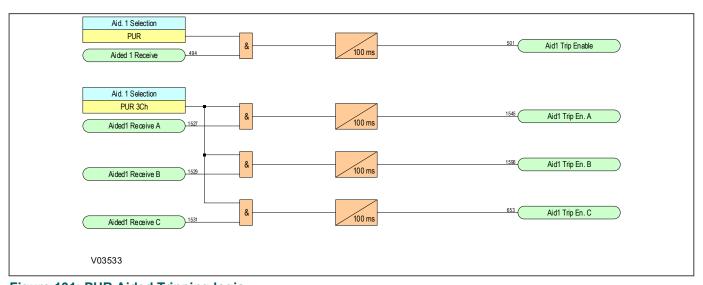

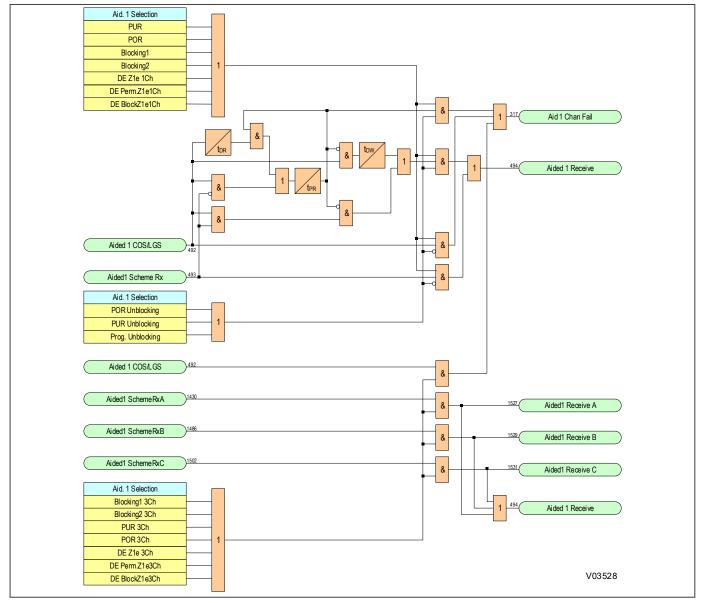

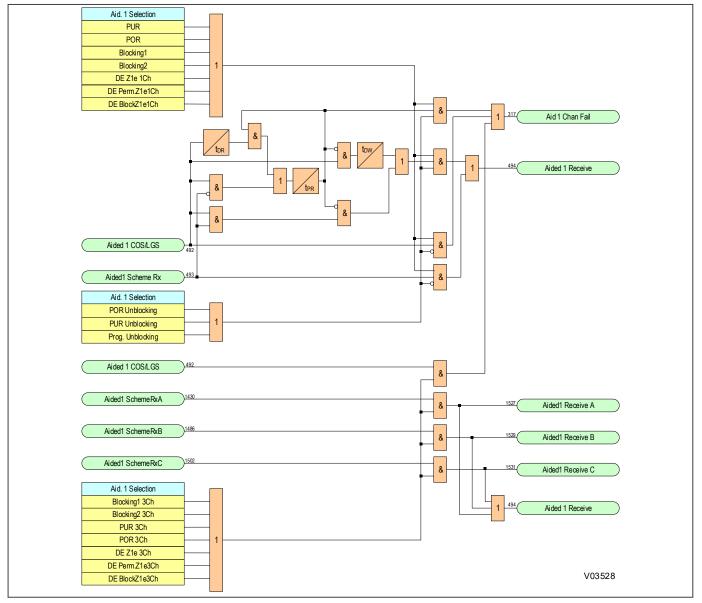

| 8.3.8.2           | Carrier Aided Schemes Receive Logic       | 233 |

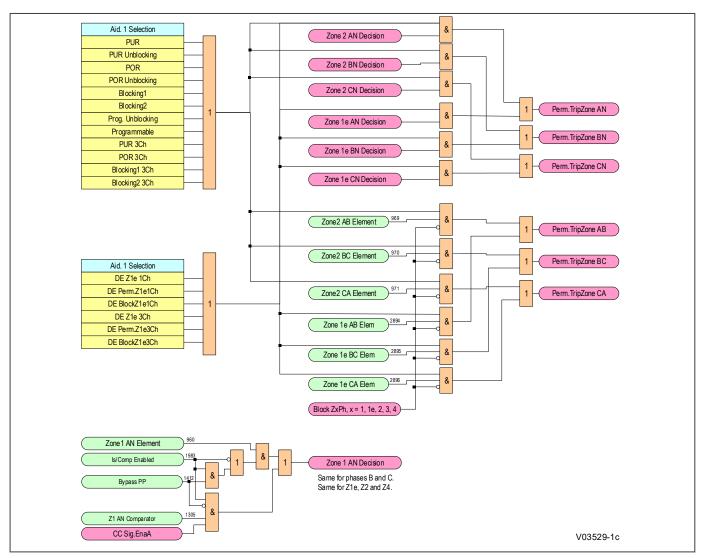

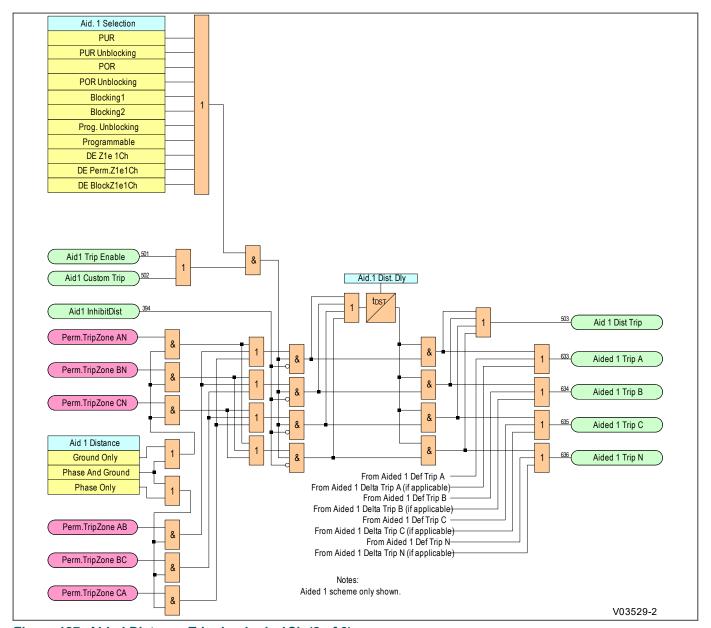

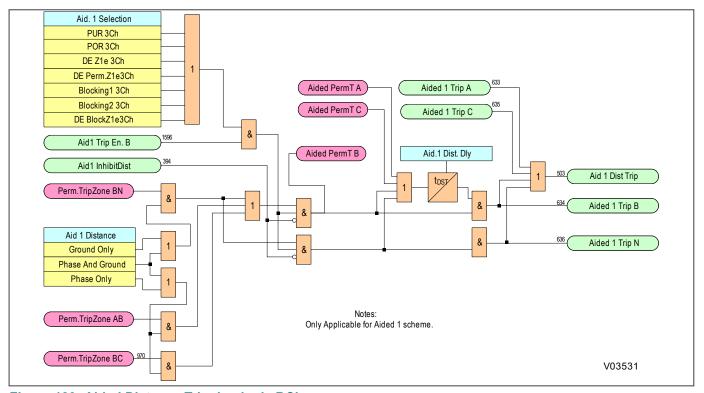

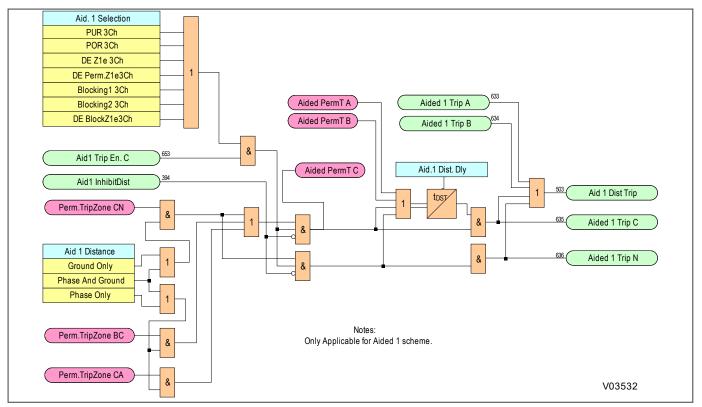

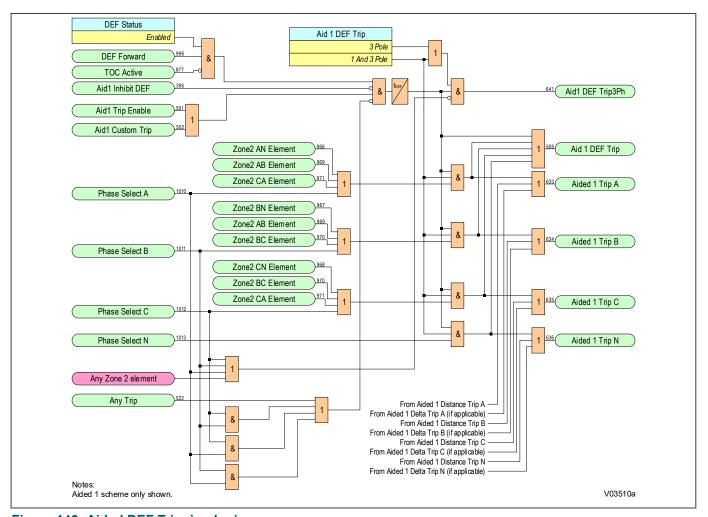

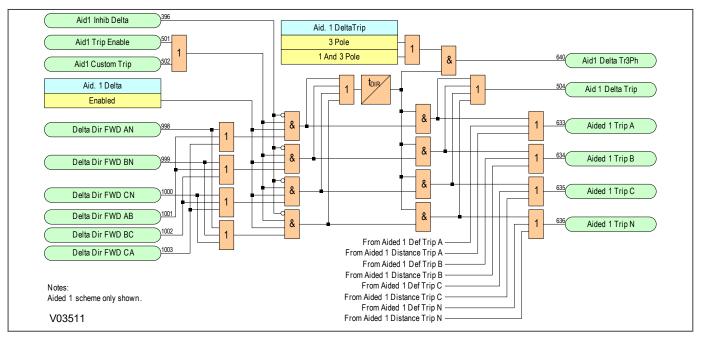

| 8.3.8.3           | Aided Distance Tripping Logic             | 234 |

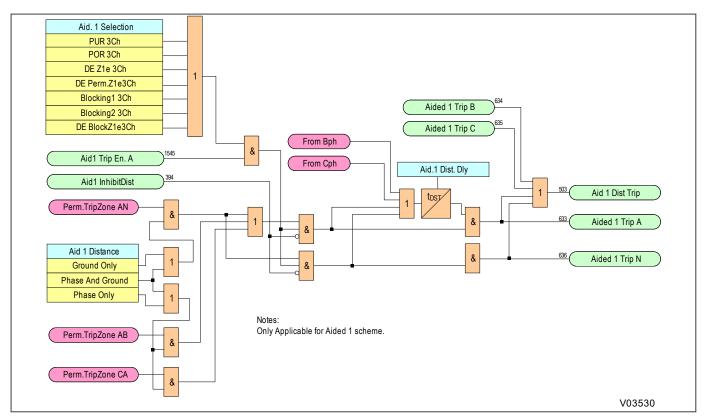

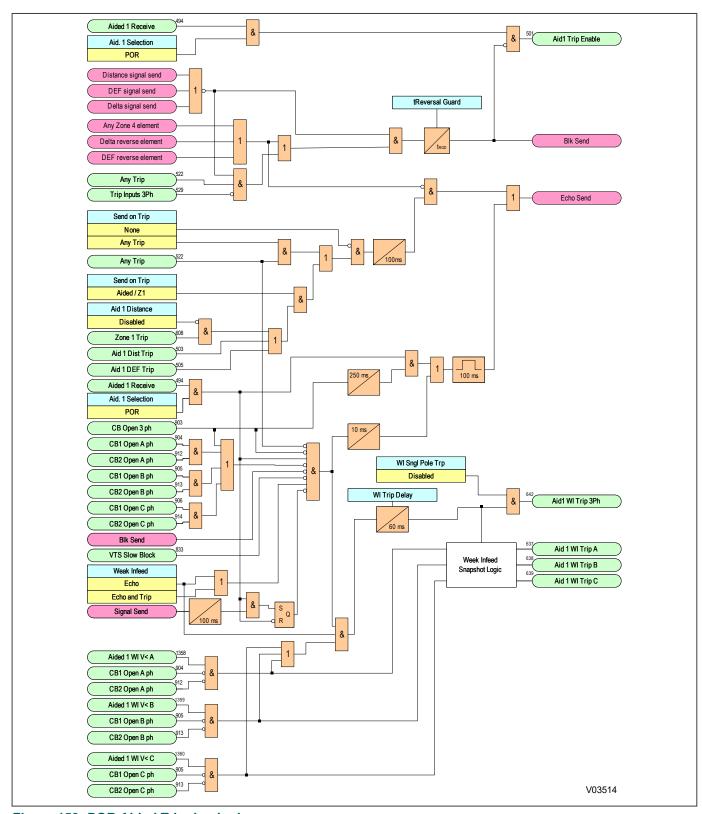

| 8.3.8.4           | PUR Aided Tripping logic                  | 237 |

| 8.3.8.5           | POR Aided Tripping logic                  | 238 |

| 8.3.8.6           | POR Aided Tripping logic                  | 242 |

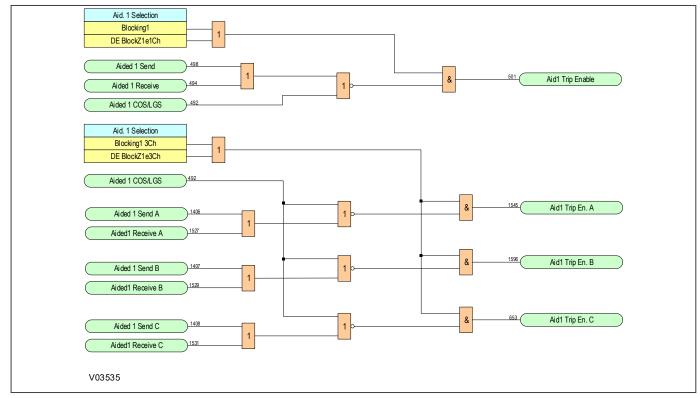

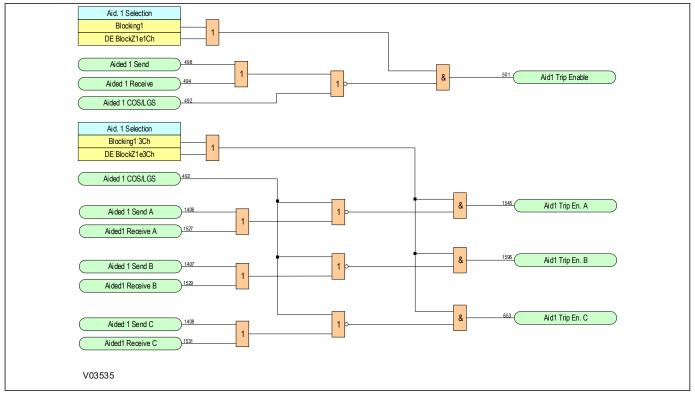

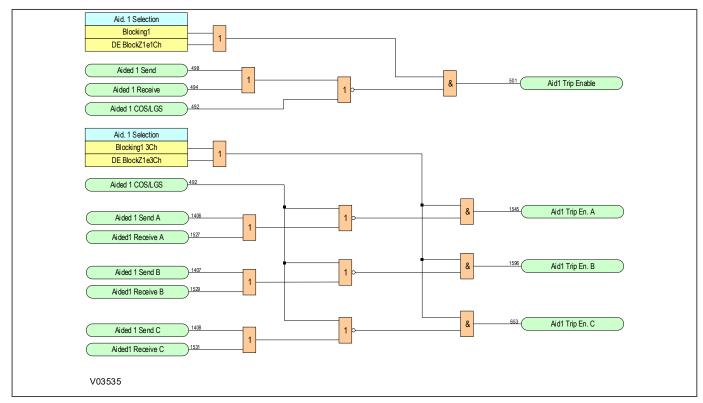

| 8.3.8.7           | Aided Scheme Blocking 1 Tripping logic    | 243 |

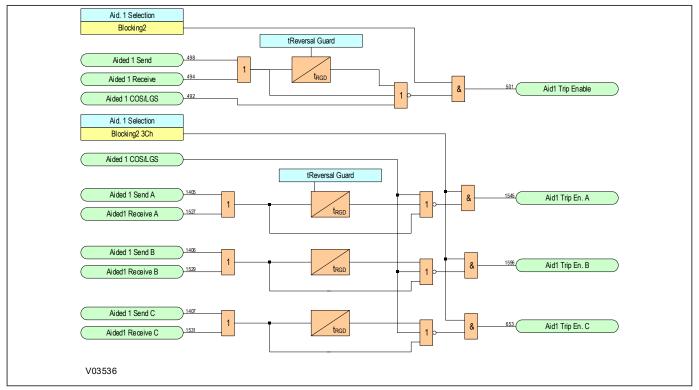

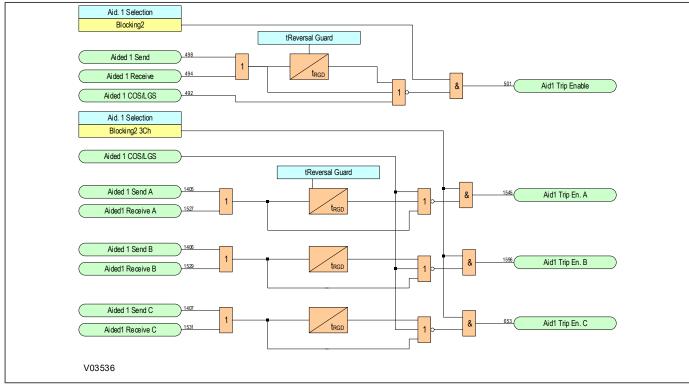

| 8.3.8.8           | Aided Scheme Blocking 2 Tripping logic    | 244 |

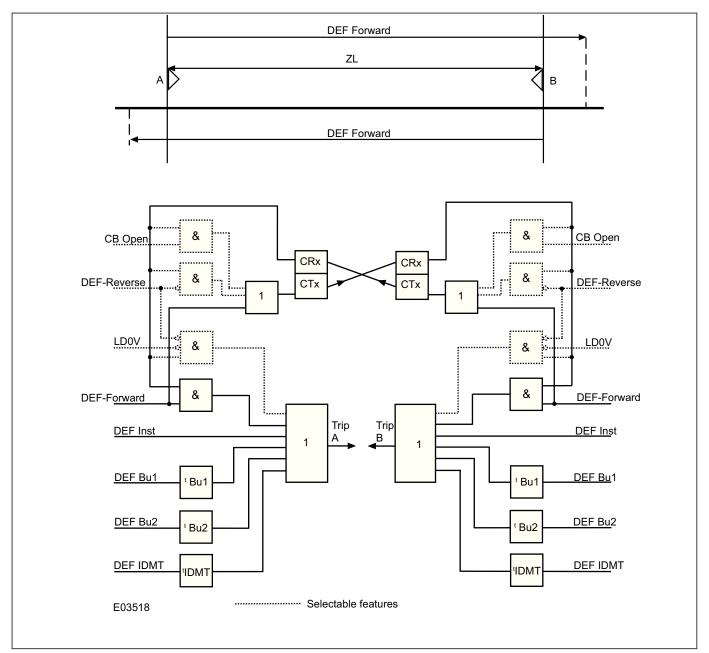

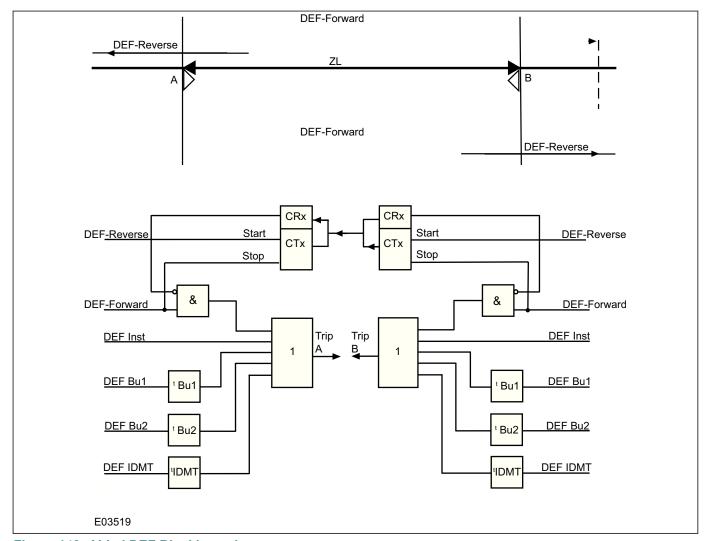

| 8.4               | Aided DEF Scheme Logic                    | 245 |

| 8.4.1             | Aided DEF Introduction                    | 245 |

| 8.4.2             | Implementation                            | 245 |

| 8.4.3             | Aided DEF Polarization                    | 245 |

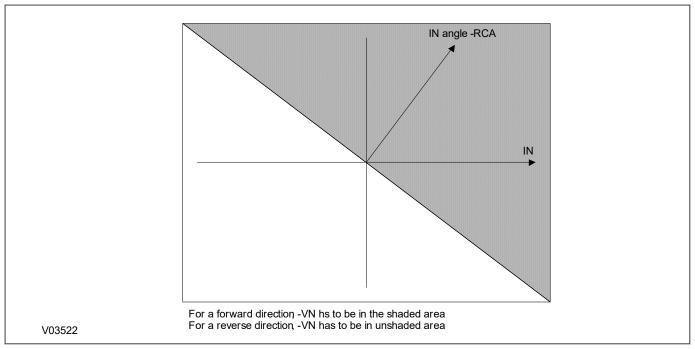

| 8.4.3.1           | Zero Sequence Polarizing                  | 246 |

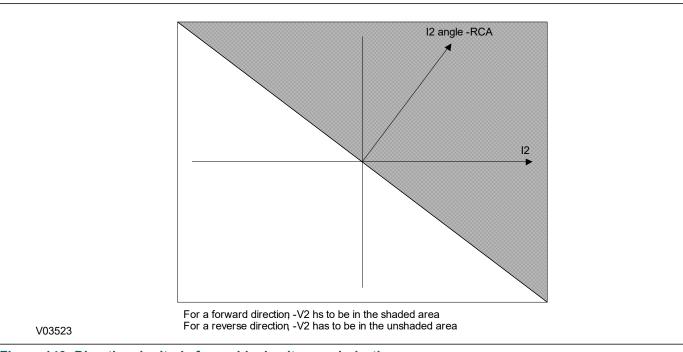

| 8.4.3.2           | Negative Sequence Polarizing              | 247 |

| 8.4.4             | Aided DEF Setting Guidelines              | 248 |

| 8.4.5             | Aided DEF POR Scheme                      | 249 |

| 8.4.6             | Aided DEF Blocking Scheme                 | 250 |

| 8.4.7             | Aided DEF Logic Diagrams                  | 251 |

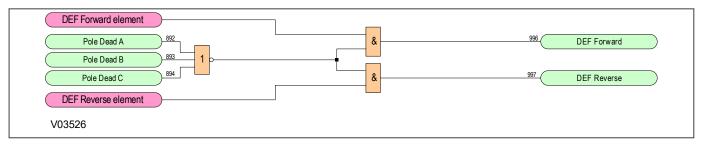

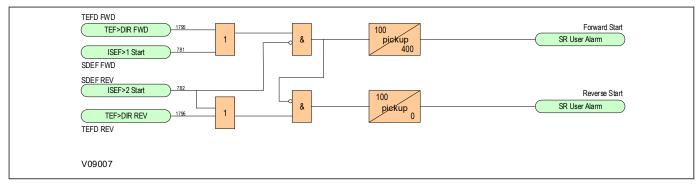

| 8.4.7.1           | DEF Directional Signals                   | 251 |

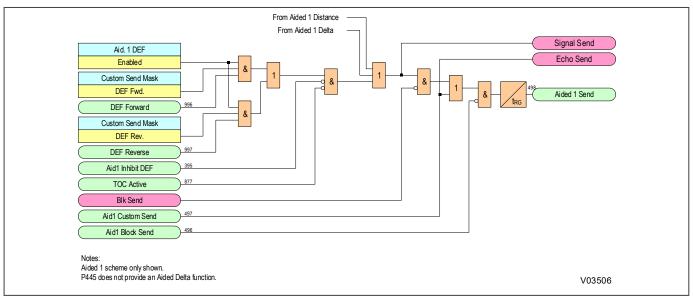

| 8.4.7.2           | Aided DEF Send Logic                      | 252 |

| 8.4.7.3           | Carrier Aided Schemes Receive Logic       | 253 |

| 8.4.7.4           | Aided DEF Tripping Logic                  | 254 |

| 8.4.7.5           | POR Aided Tripping logic                  | 255 |

| 8.4.7.6           | POR Aided Tripping logic                  | 257 |

| 8.4.7.7           | Aided Scheme Blocking 1 Tripping logic    | 258 |

| 8.4.7.8           | Aided Scheme Blocking 2 Tripping logic    | 259 |

| 8.5               | Aided Delta Scheme Logic                  | 260 |

| 8.5.1             | Aided Delta POR Scheme                    | 260 |

| 8.5.2             | Aided Delta Blocking Scheme               | 261 |

| 8.5.3             | Aided Delta Logic Diagrams                | 263 |

| 8.5.3.1           | Aided Delta Send Logic                    | 263 |

| 8.5.3.2           | Carrier Aided Schemes Receive Logic       | 264 |

| 8.5.3.3           | Aided Delta Tripping Logic                | 265 |

| 8.5.3.4           | POR Aided Tripping logic                  | 266 |

| 8.5.3.5           | POR Aided Tripping logic                  | 268 |

| 8.5.3.6           | Aided Scheme Blocking 1 Tripping logic    | 269 |

| 8.5.3.7           | Aided Scheme Blocking 2 Tripping logic    | 270 |

| 8.6               | DE Teleprotection Schemes                 | 271 |

| 8.6.1             | DE Scheme Description                     | 271 |

| 8.7               | Application Notes                         | 273 |

| 8.7.1             | Aided Distance PUR Scheme                 | 273 |

| 8.7.2             | Aided Distance POR Scheme                 | 273 |

| 8.7.3             | Aided Distance Blocking Scheme            | 273 |

| 8.7.4             | Aided DEF POR Scheme                      | 274 |

| 8.7. <del>5</del> | Aided DEF Blocking Scheme                 | 274 |

|                   | <u> </u>                                  |     |

| 8.7.6<br>9.7.7    | Aided Delta POR Scheme                    | 274 |

| 8.7.7             | Aided Delta Blocking Scheme               | 274 |

vi P54-TM-EN-2

| P54 | Contents |

|-----|----------|

|-----|----------|

| 8.7.8                | Teed Feeder Applications                                                 | 275                                |

|----------------------|--------------------------------------------------------------------------|------------------------------------|

| 8.7.8.1              | POR Schemes for Teed Feeders                                             | 270                                |

| 8.7.8.2              | PUR Schemes for Teed Feeders                                             | 27                                 |

| 8.7.8.3              | Blocking Schemes for Teed Feeders                                        | 278                                |

| Chapte               | r 9 Non-Aided Schemes                                                    | 281                                |

| 9.1                  | Chapter Overview                                                         | 282                                |

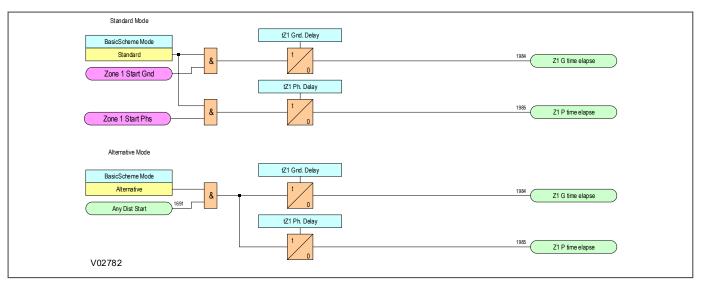

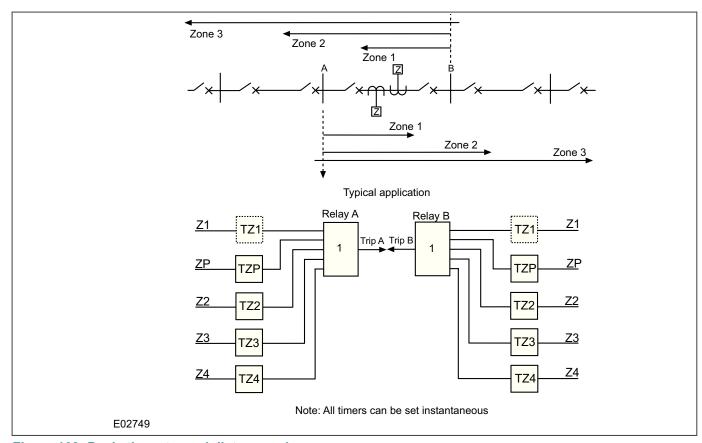

| 9.2                  | Non-Aided Schemes                                                        | 28:                                |

| 9.3                  | Basic Schemes                                                            | 284                                |

| 9.3.1                | Basic Scheme Modes                                                       | 284                                |

| 9.3.2                | Basic Scheme Setting                                                     | 286                                |

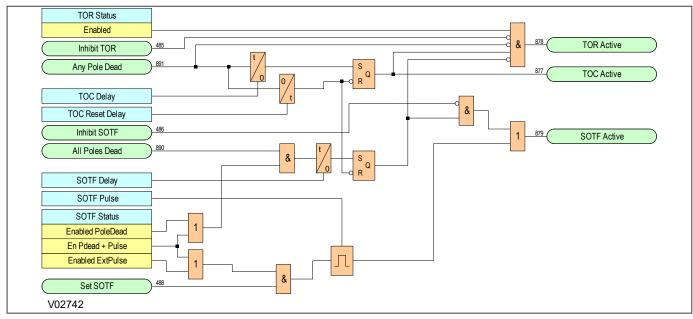

| 9.4                  | Trip On Close Schemes                                                    | 288                                |

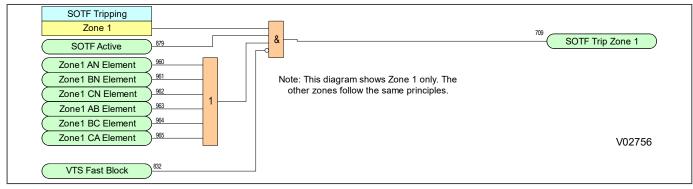

| 9.4.1                | Switch On To Fault (SOTF)                                                | 289                                |

| 9.4.1.1              | Switch Onto Fault Mode                                                   | 289                                |

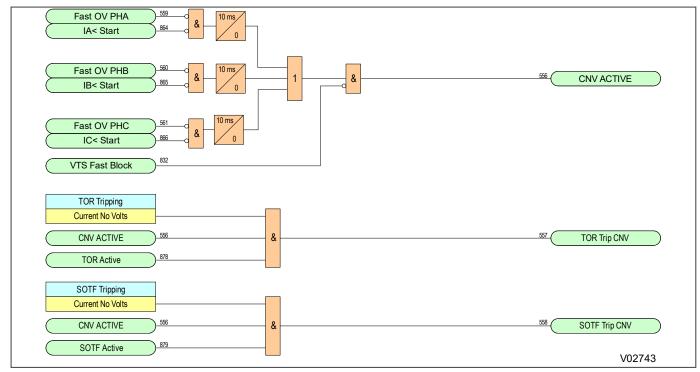

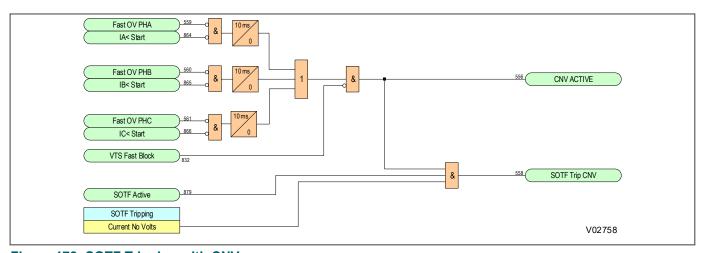

| 9.4.1.2              | SOTF Tripping                                                            | 290                                |

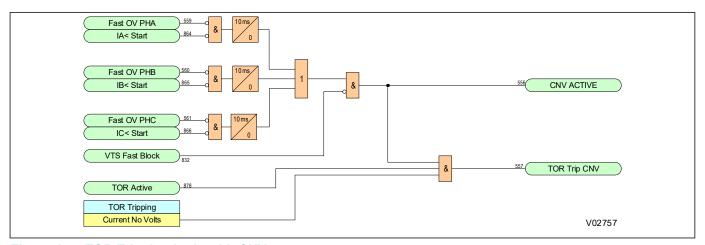

| 9.4.1.3              | SOTF Tripping with CNV                                                   | 290                                |

| 9.4.2                | Trip On Reclose (TOR)                                                    | 290                                |

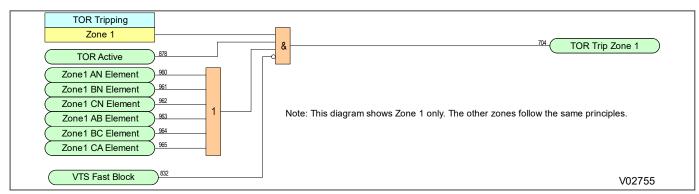

| 9.4.2.1<br>9.4.2.2   | Trip On Reclose Mode TOR Tripping Logic for Appropriate Zones            | 29 <sup>-</sup><br>29 <sup>-</sup> |

| 9.4.2.2              | TOR Tripping Logic for Appropriate Zones  TOR Tripping Logic with CNV    | 29                                 |

| 9.4.3                | Polarisation during Circuit Engergisation                                | 292                                |

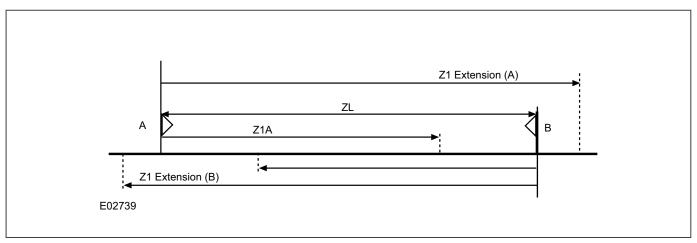

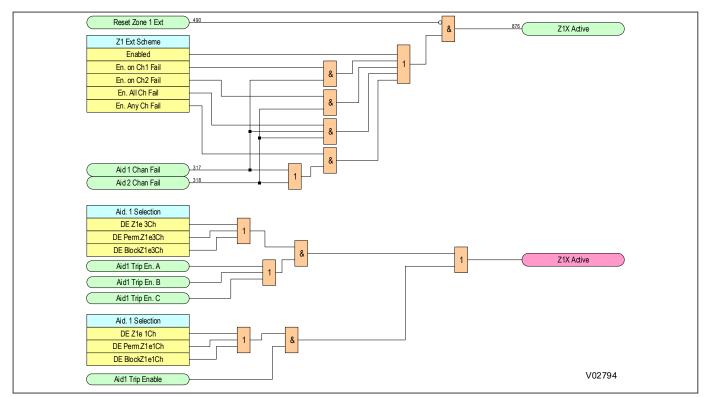

| 9.5                  | Zone 1 Extension Scheme                                                  | 293                                |

| 9.6                  | Loss of Load Scheme                                                      | 299                                |

|                      |                                                                          |                                    |

| Chapte               | r 10 Power Swing Functions                                               | 297                                |

| 10.1                 | Chapter Overview                                                         | 298                                |

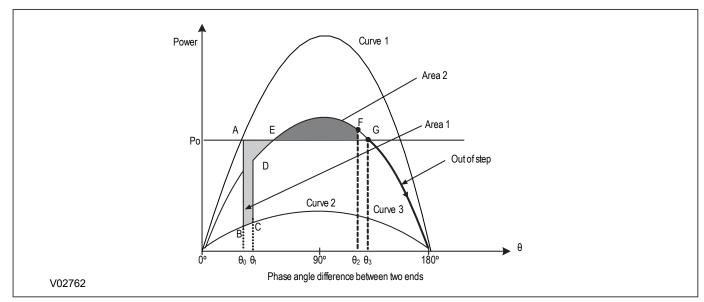

| 10.2                 | Introduction to Power Swing Blocking                                     | 299                                |

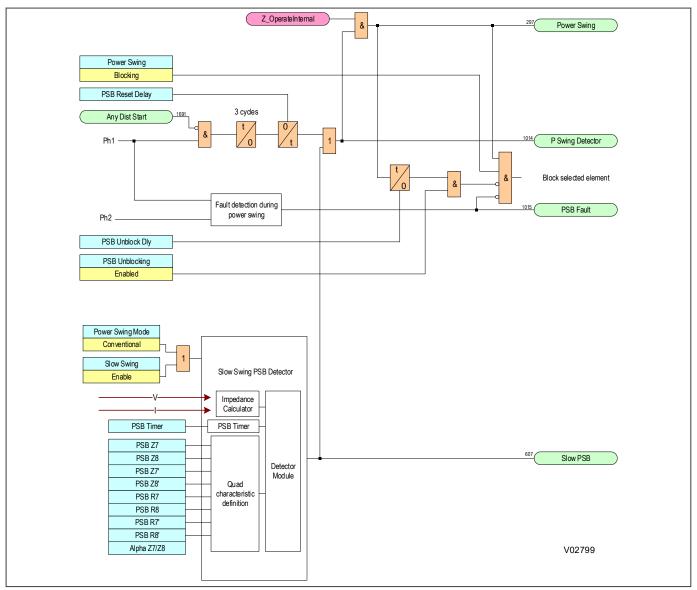

| 10.3                 | Power Swing Blocking                                                     | 30                                 |

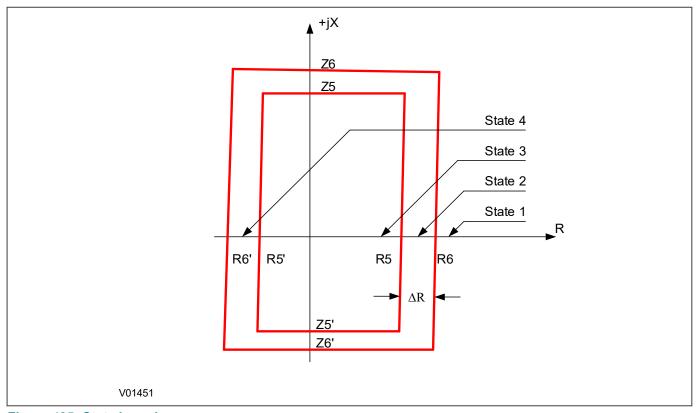

| 10.3.1               | Power Swing Detection                                                    | 30                                 |

| 10.3.1.1             | Settings-Free Power Swing Detection                                      | 30                                 |

| 10.3.1.2<br>10.3.1.3 | Slow Power Swing Detection Power Swing Detection (Alarming and Blocking) | 30 <sub>4</sub><br>30 <sub>5</sub> |

| 10.3.1.3             | Detection of a Fault During a Power Swing                                | 309                                |

| 10.3.3               | Power Swing Blocking Configuration                                       | 310                                |

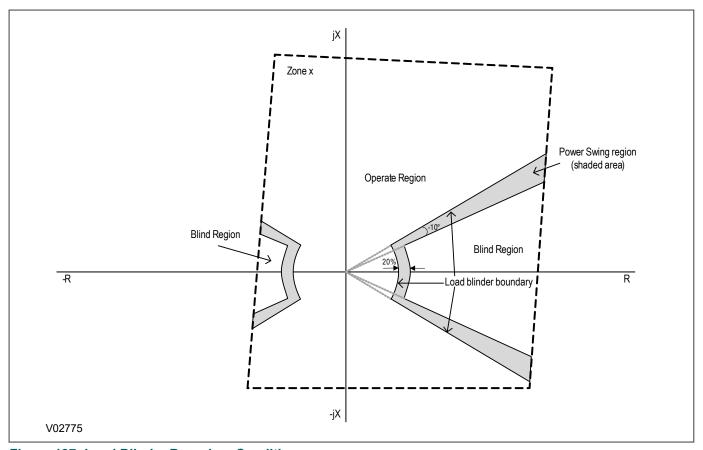

| 10.3.4               | Power Swing Load Blinding Boundary                                       | 31′                                |

| 10.3.5               | Power Swing Blocking Logic                                               | 31                                 |

| 10.3.6               | Power Swing Blocking Setting Guidelines                                  | 312                                |

| 10.3.6.1             | Setting the Resistive Limits                                             | 31:                                |

| 10.3.6.2             | Setting the Reactive Limits                                              | 31:                                |

| 10.3.6.3             | PSB Timer Setting Guidelines                                             | 314                                |

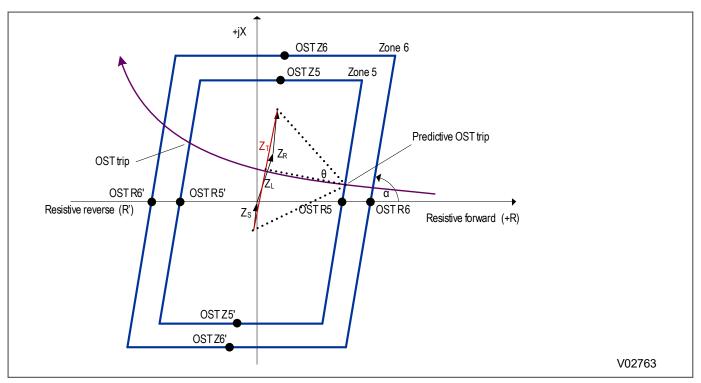

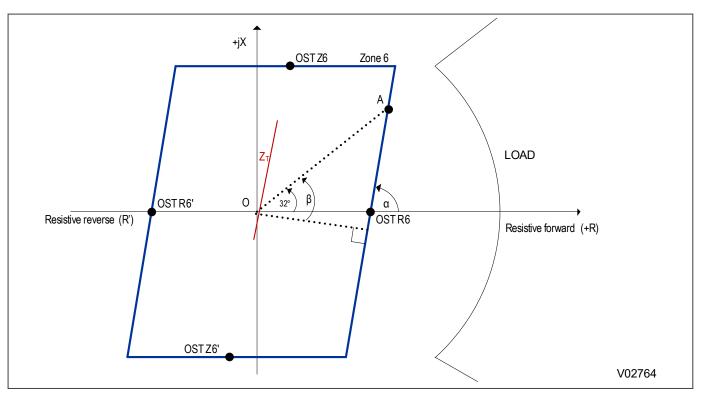

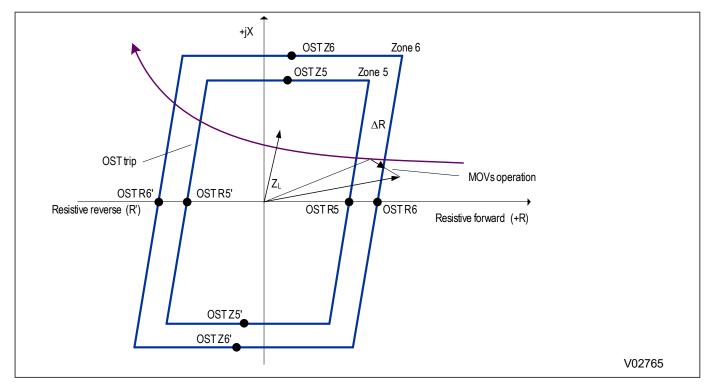

| 10.4                 | Out of Step Protection                                                   | 310                                |

| 10.4.1               | Out of Step Detection                                                    | 316                                |

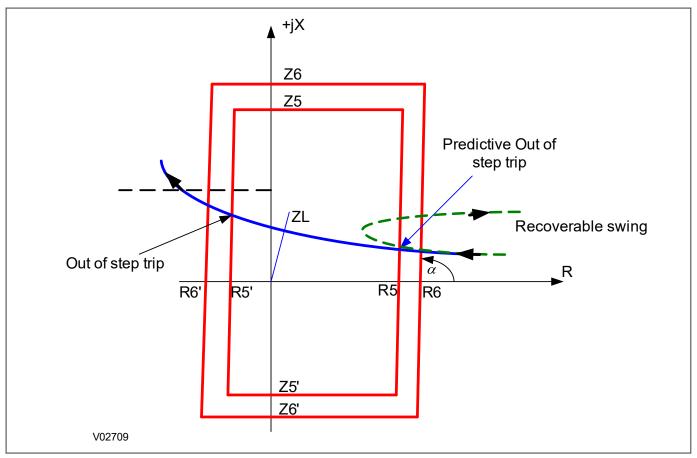

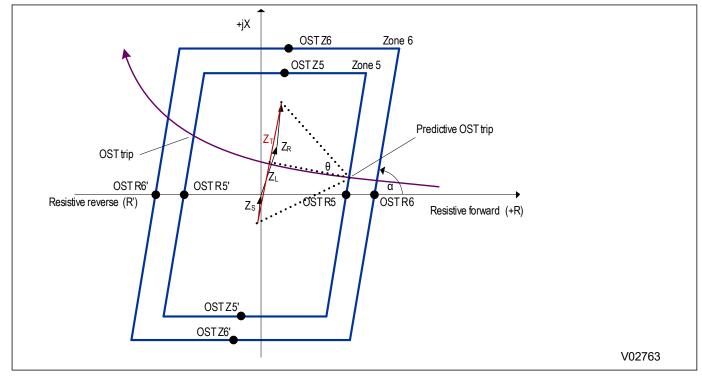

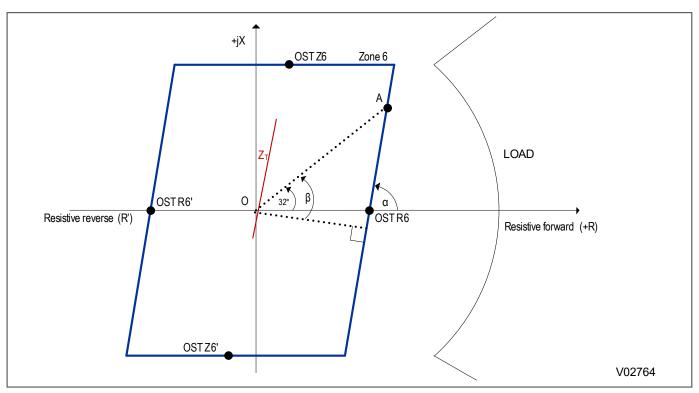

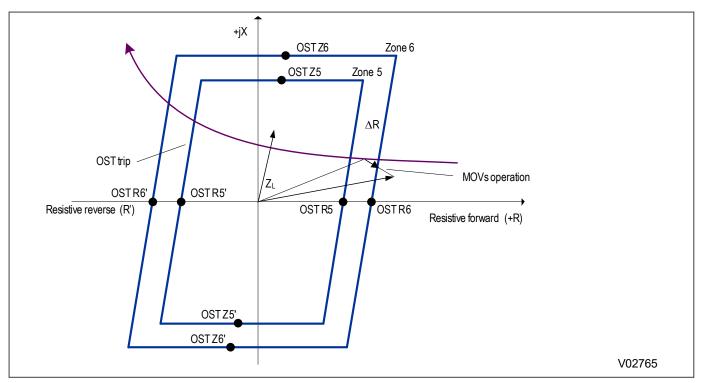

| 10.4.2               | Out of Step Protection Operating Principle                               | 317                                |

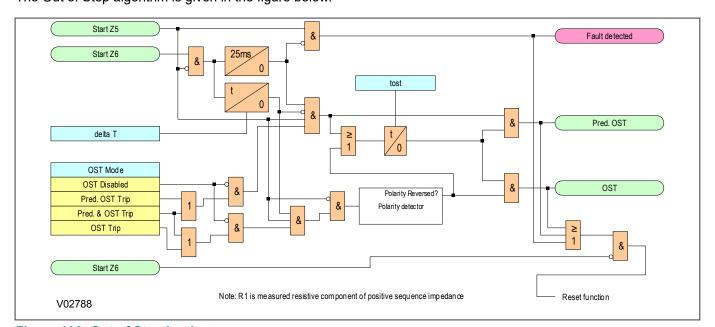

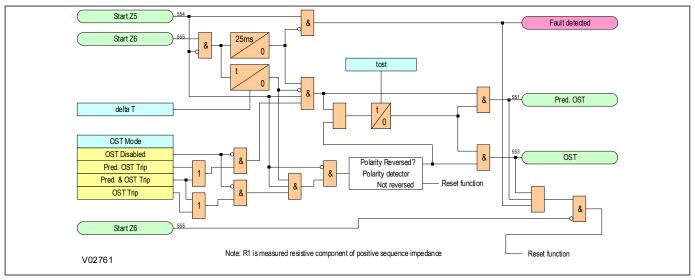

| 10.4.3               | Out of Step Logic Diagram                                                | 318                                |

| 10.4.4               | OST Application Notes                                                    | 318                                |

| 10.4.4.1<br>10.4.4.2 | Setting the OST Mode                                                     | 318<br>323                         |

| 10.4.4.2             | Power Swing Alarming and Blocking Critical Stability Angle               | 324                                |

| Chapte               | r 11 Autoreclose                                                         | 331                                |

| 11.1                 | Chapter Overview                                                         | 332                                |

| 11.2                 | Introduction to Autoreclose                                              | 333                                |

| 11.2.1               | Adaptive Autoreclose Overview                                            | 333                                |

| 11.3                 | Autoreclose Implementation                                               | 330                                |

|                      |                                                                          |                                    |

P54-TM-EN-2 vii

| 11.3.1    | Autoreclose Logic Inputs from External Sources              | 337 |

|-----------|-------------------------------------------------------------|-----|

| 11.3.1.1  | Circuit Breaker Healthy Input                               | 337 |

| 11.3.1.2  | Inhibit Autoreclose Input                                   | 337 |

| 11.3.1.3  | Block Autoreclose Input                                     | 337 |

| 11.3.1.4  | Reset Lockout Input                                         | 338 |

| 11.3.1.5  | Pole Discrepancy Input                                      | 338 |

| 11.3.1.6  |                                                             | 338 |

|           | External Trip Indication                                    |     |

| 11.3.2    | Autoreclose Logic Inputs                                    | 338 |

| 11.3.2.1  | Trip Initiation Signals                                     | 338 |

| 11.3.2.2  | Circuit Breaker Status Inputs                               | 338 |

| 11.3.2.3  | System Check Signals                                        | 338 |

| 11.3.3    | Autoreclose Logic Outputs                                   | 338 |

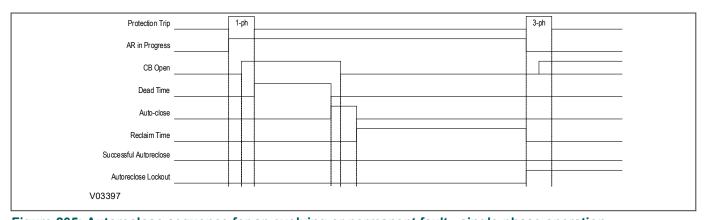

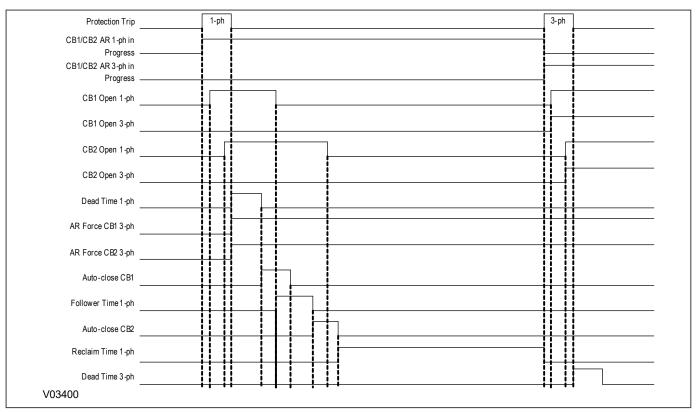

| 11.3.4    | Autoreclose Operating Sequence                              | 339 |

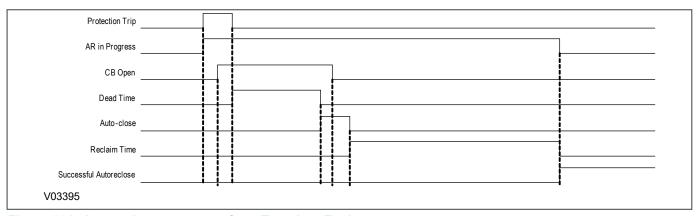

| 11.3.4.1  | AR Timing Sequence - Transient Fault                        | 339 |

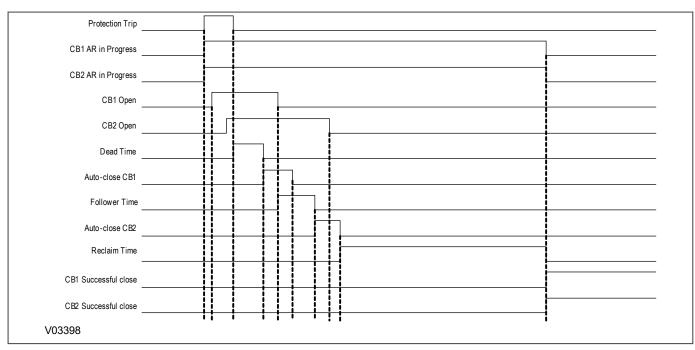

| 11.3.4.2  | AR Timing Sequence - Transient Fault Dual CB                | 339 |

| 11.3.4.3  |                                                             | 340 |

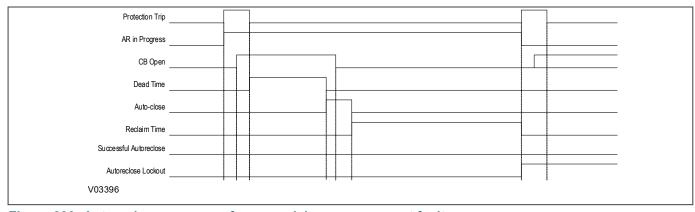

|           | AR Timing Sequence - Evolving/Permanent Fault               |     |

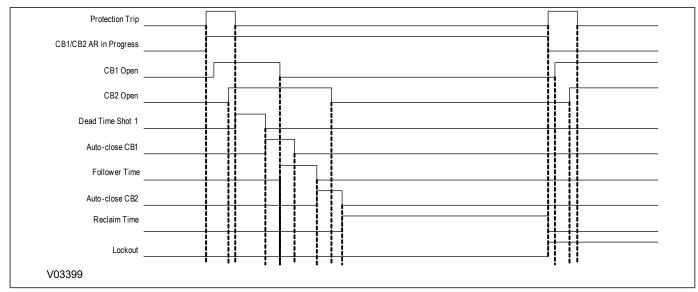

| 11.3.4.4  | AR Timing Sequence - Evolving/Permanent Fault Dual CB       | 341 |

| 11.3.4.5  | AR Timing Sequence - Evolving/Permanent Fault Single-phase  | 341 |

| 11.3.4.6  | AR Timing Sequence - Persistent Fault                       | 341 |

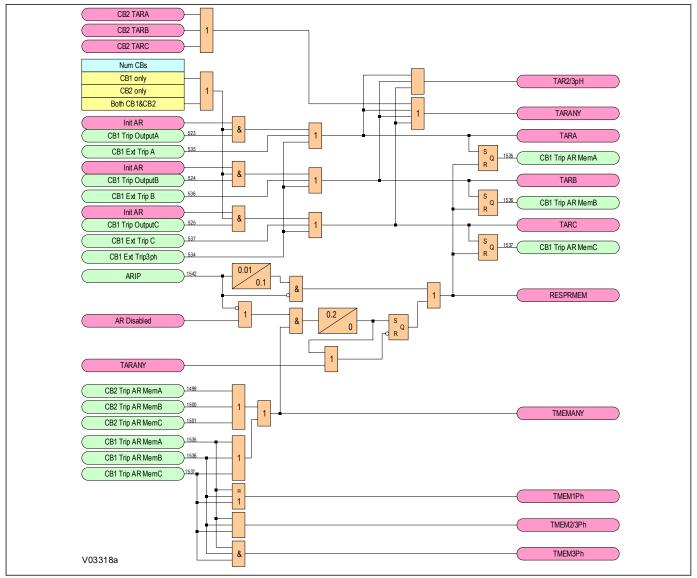

| 11.4      | Logic Modules (Single CB)                                   | 343 |

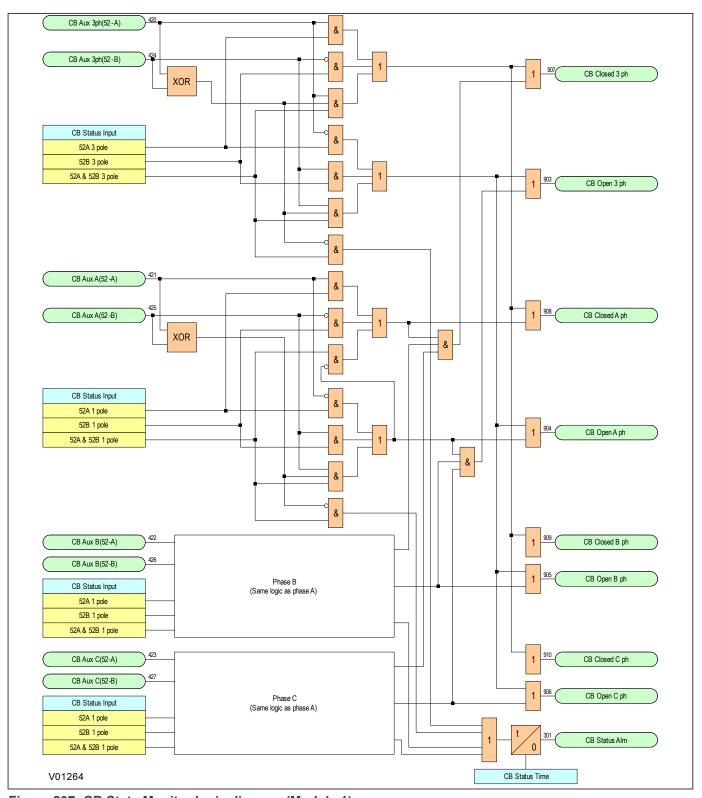

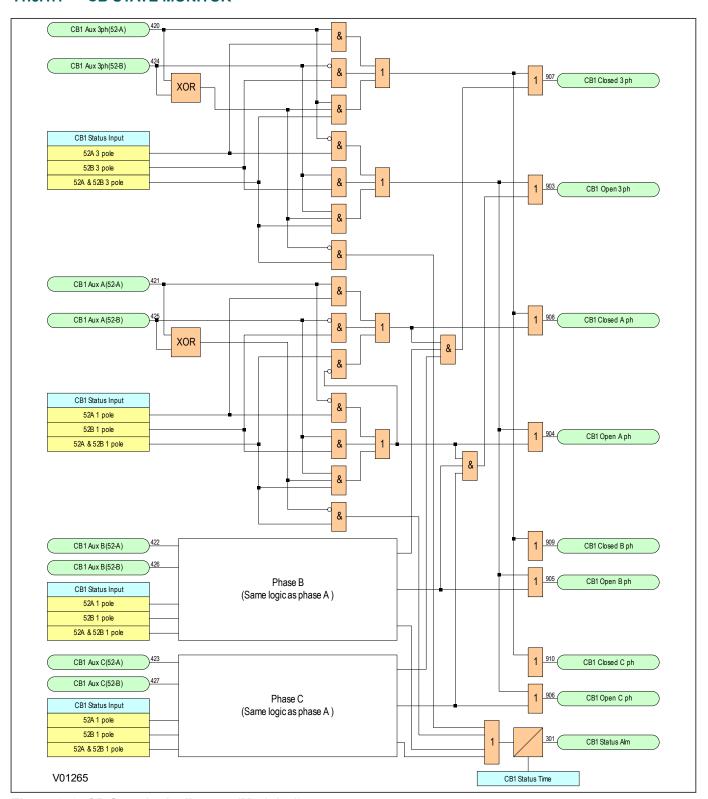

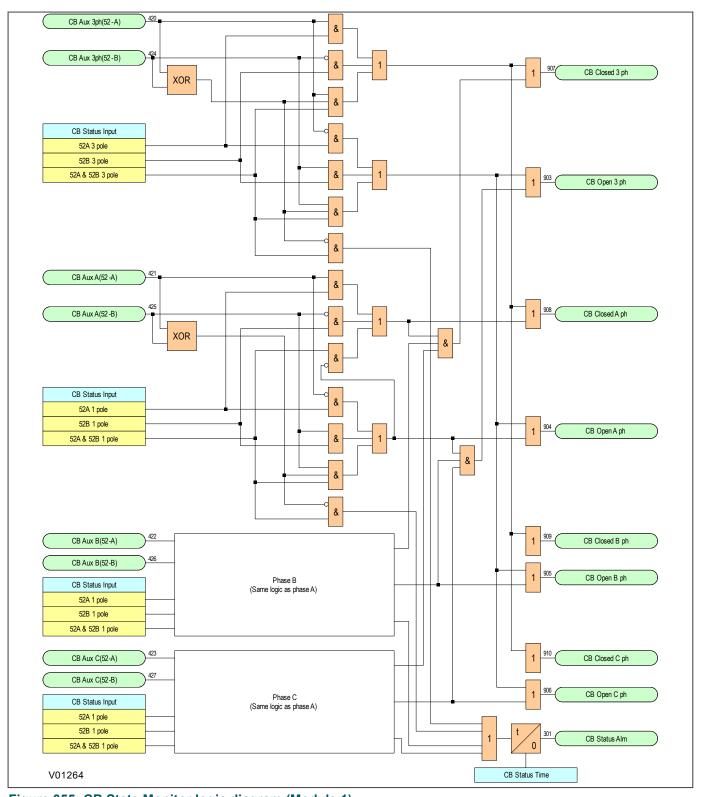

| 11.4.1    | Circuit Breaker Status Monitor                              | 343 |

| 11.4.1.1  | CB State Monitor Logic diagram                              | 344 |

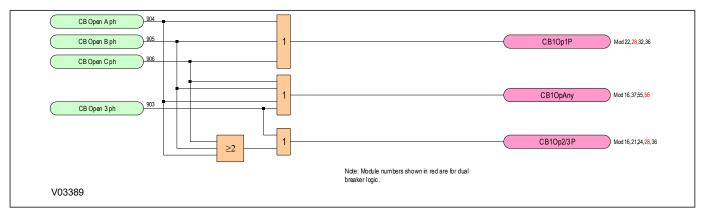

| 11.4.2    | Circuit Breaker Open Logic                                  | 345 |

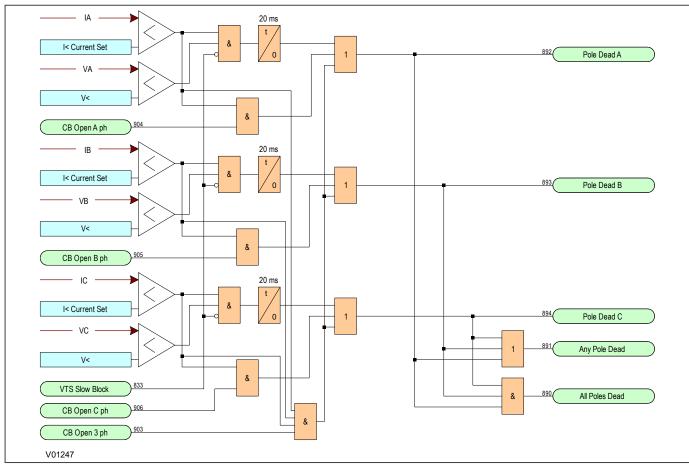

| 11.4.2.1  | Circuit Breaker Open Logic Diagram                          | 345 |

|           |                                                             |     |

| 11.4.3    | Circuit Breaker in Service Logic                            | 345 |

| 11.4.3.1  | Circuit Breaker in Service Logic Diagram                    | 345 |

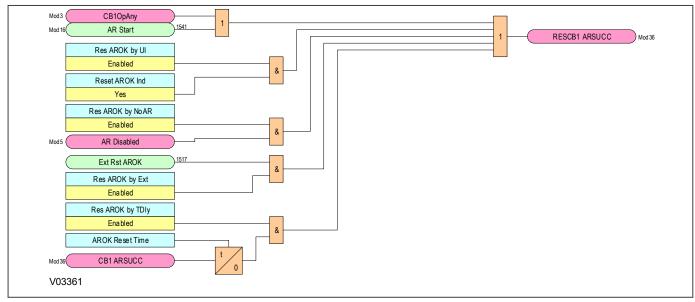

| 11.4.3.2  | Autoreclose OK Logic Diagram                                | 346 |

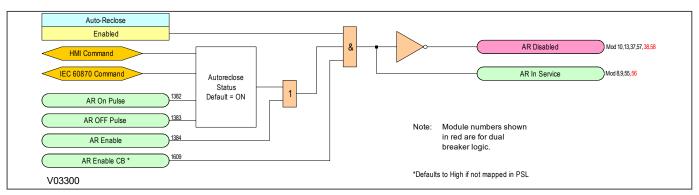

| 11.4.4    | Autoreclose Enable                                          | 346 |

| 11.4.4.1  | Autoreclose Enable Logic Diagram                            | 346 |

| 11.4.5    | Autoreclose Modes                                           | 346 |

| 11.4.5.1  | Single-Phase and Three-Phase Autoreclose                    | 347 |

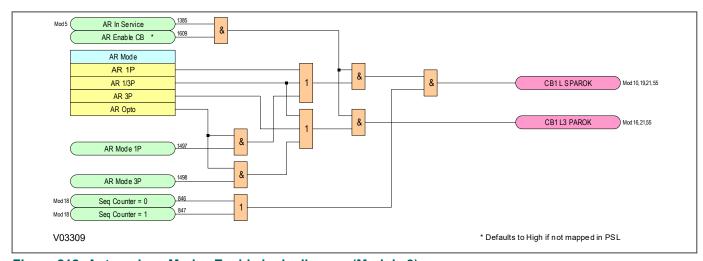

| 11.4.5.2  | Autoreclose Modes Enable Logic Diagram                      | 347 |

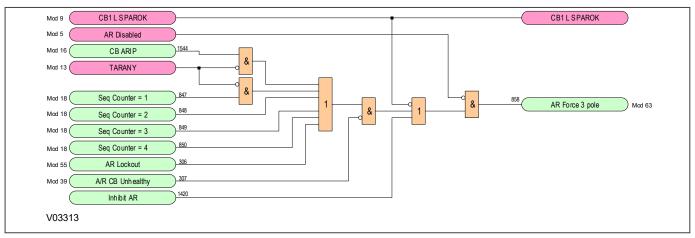

| 11.4.6    | AR Force Three-Phase Trip Logic                             | 348 |

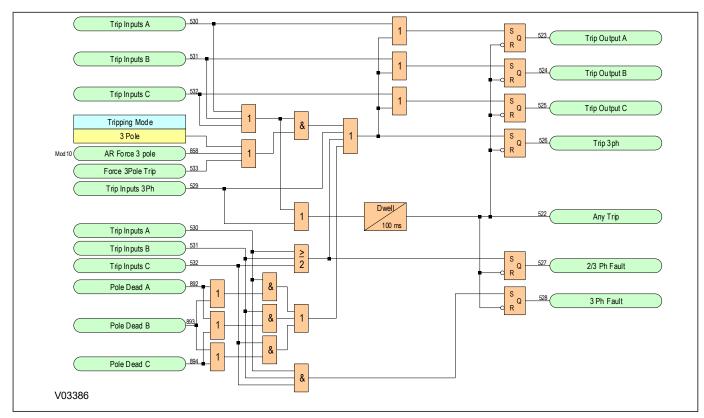

| 11.4.6.1  | AR Force Three-Phase Trip Logic Diagram                     | 348 |

|           |                                                             |     |

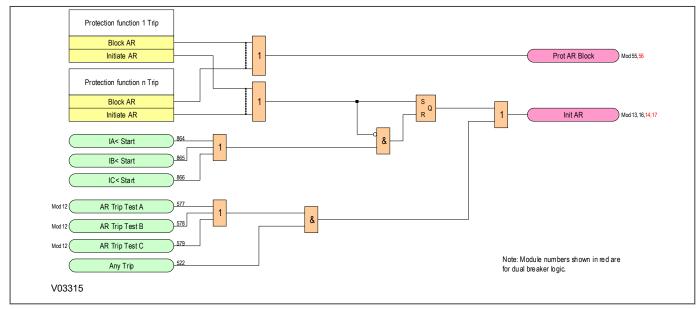

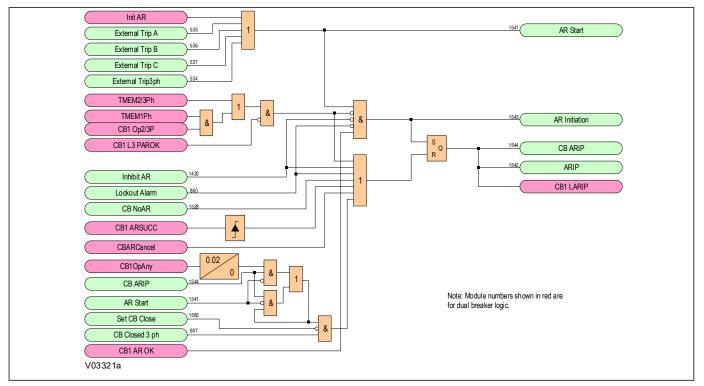

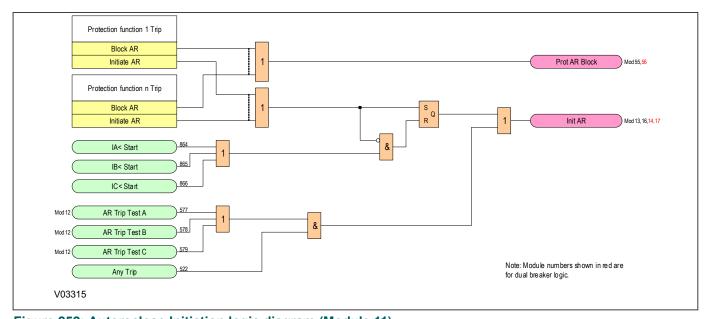

| 11.4.7    | Autoreclose Initiation Logic                                | 348 |

| 11.4.7.1  | Autoreclose Initiation Logic Diagram                        | 349 |

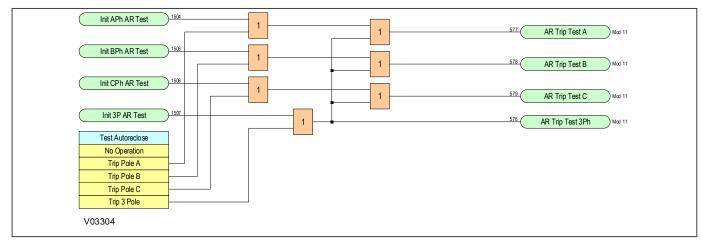

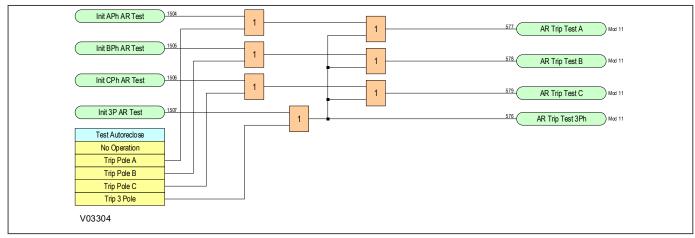

| 11.4.7.2  | Autoreclose Trip Test Logic Diagram                         | 350 |

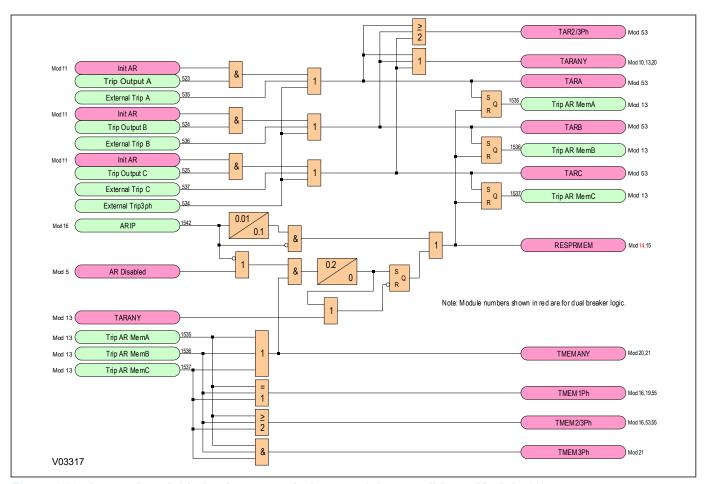

| 11.4.7.3  | AR External Trip Initiation Logic Diagram                   | 350 |

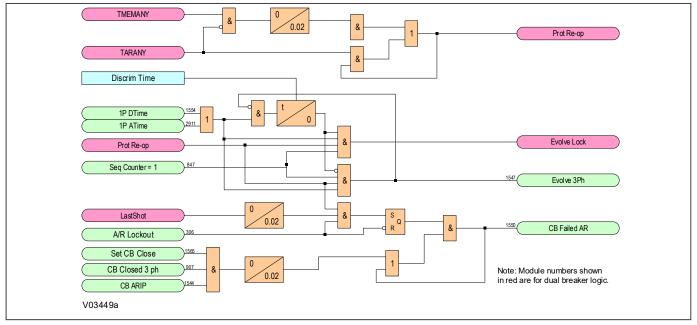

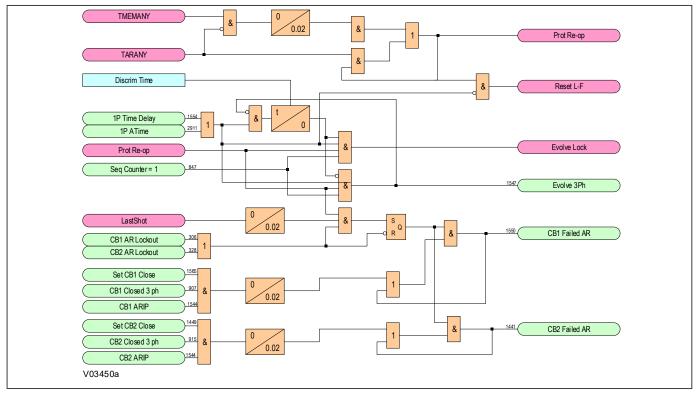

| 11.4.7.4  | Protection Reoperation and Evolving Fault Logic Diagram     | 351 |

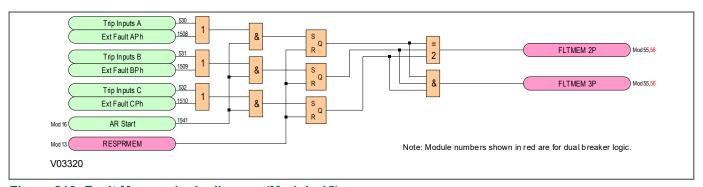

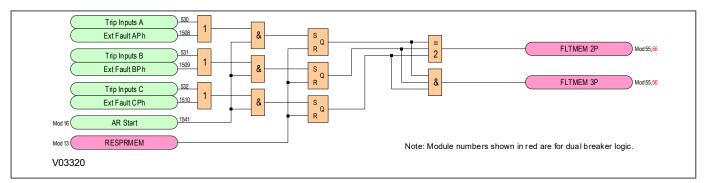

| 11.4.7.5  | Fault Memory Logic Diagram                                  | 351 |

| 11.4.8    | Autoreclose In Progress                                     | 351 |

| 11.4.8.1  | Autoreclose In Progress Logic Diagram                       | 352 |

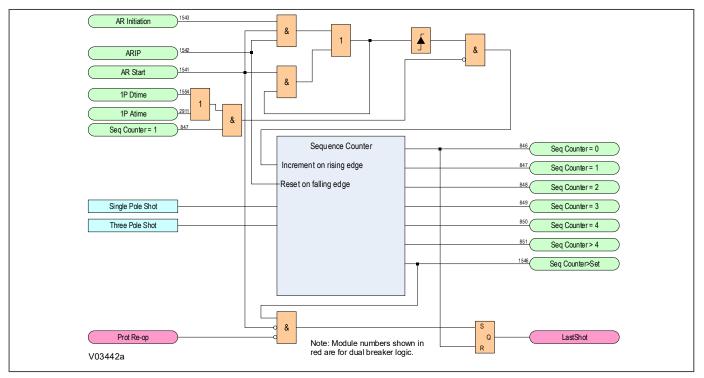

| 11.4.9    | Sequence Counter                                            | 352 |

| 11.4.9.1  | Autoreclose Sequence Counter Logic Diagram                  | 353 |

| 11.4.10   |                                                             | 353 |

|           | Autoreclose Cycle Selection                                 |     |

| 11.4.10.1 | Single-Phase Autoreclose Cycle Selection Logic Diagram      | 353 |

| 11.4.10.2 | 3-phase Autoreclose Cycle Selection                         | 353 |

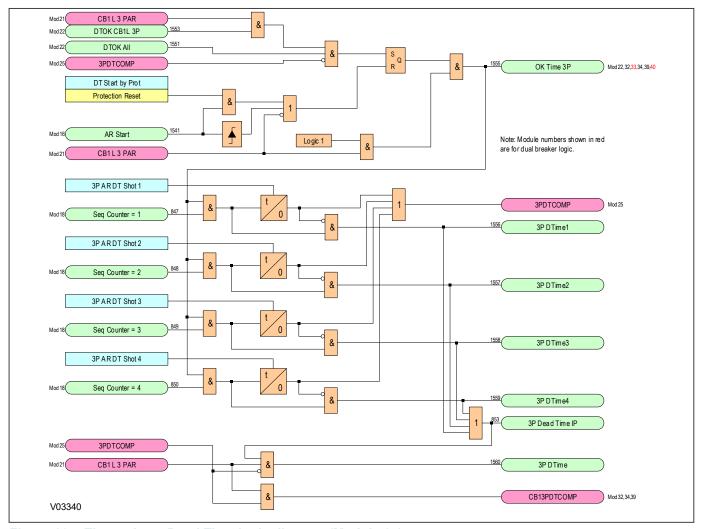

| 11.4.11   | Dead Time Control                                           | 354 |

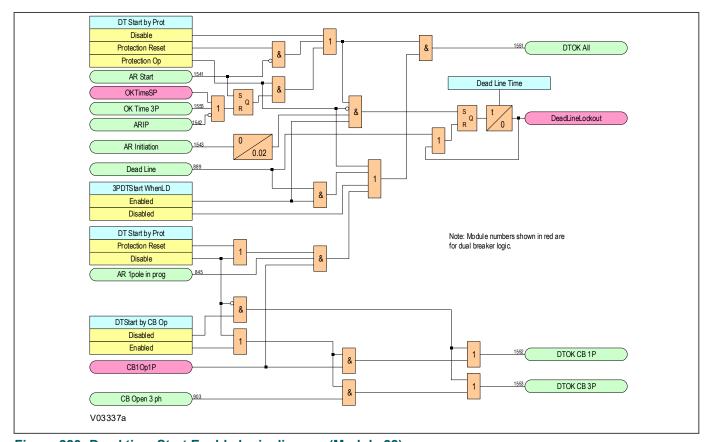

| 11.4.11.1 | Dead Time Start Enable Logic Diagram                        | 354 |

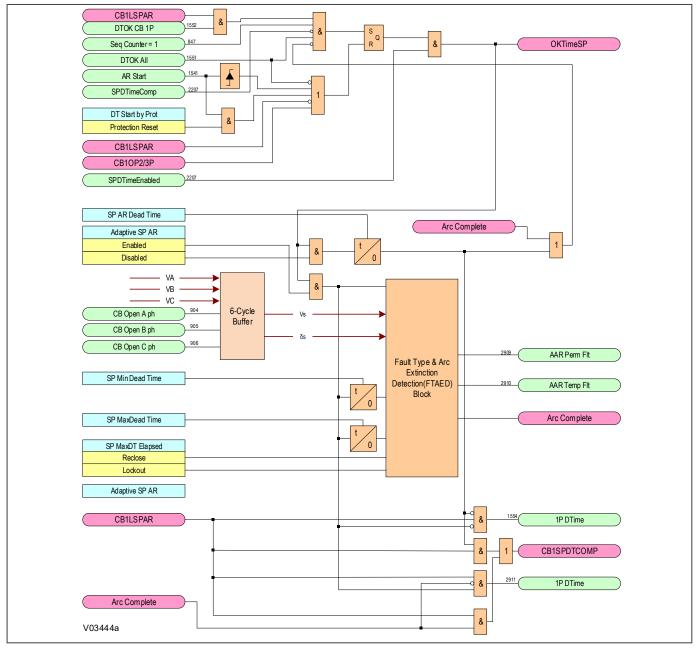

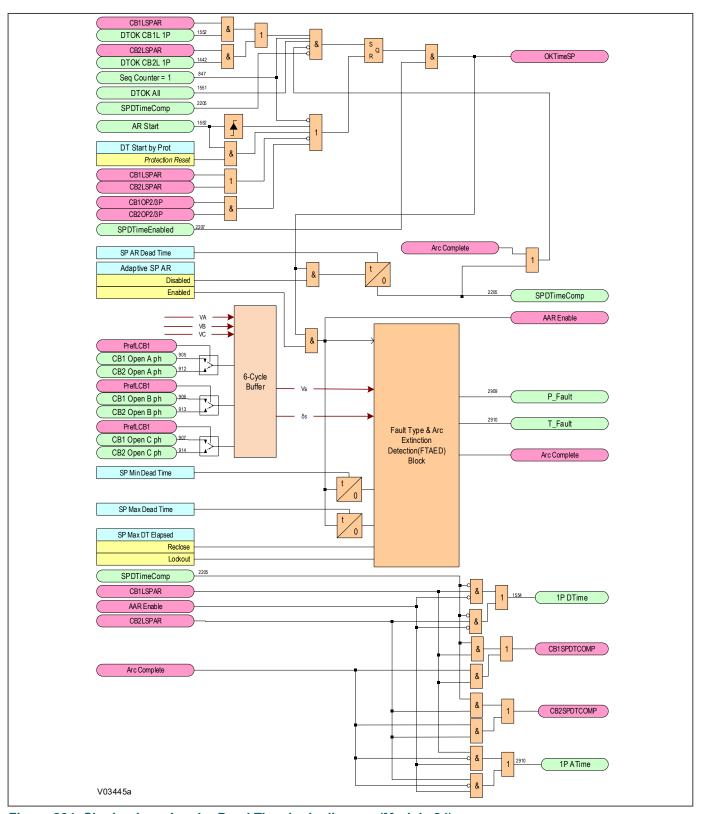

| 11.4.11.2 | Single-phase Dead Time and Adaptive Autoreclose (AAR) Logic | 355 |

| 11.4.11.3 | 1-phase Dead Time Logic Diagram                             | 356 |

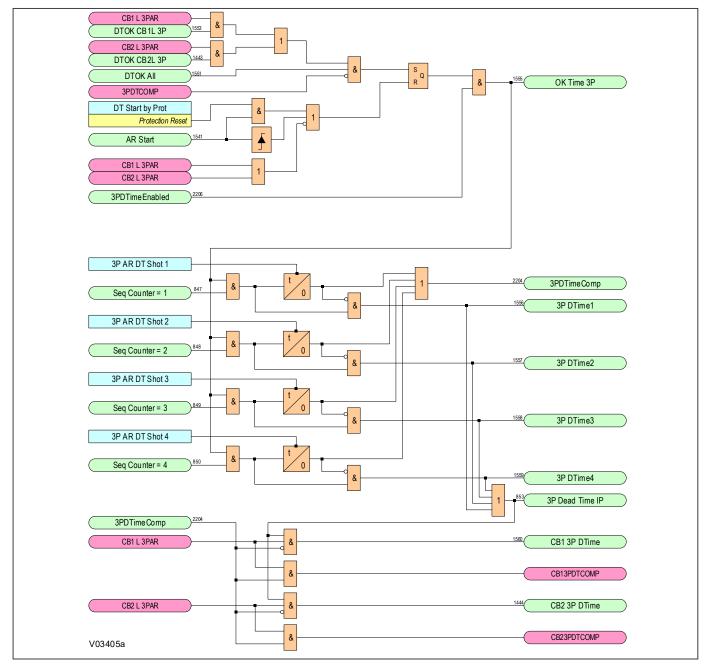

| 11.4.11.4 | 3-phase Dead Time Logic Diagram                             | 357 |

| 11.4.12   | Circuit Breaker Autoclose                                   | 357 |

| 11.4.12.1 | Circuit Breaker Autoclose Logic Diagram                     | 358 |

| 11.4.13   | Reclaim Time                                                | 358 |

|           |                                                             |     |

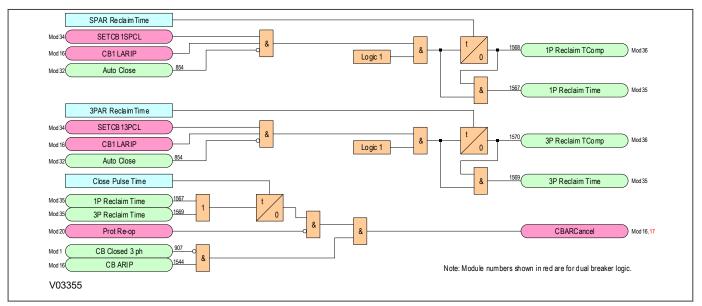

| 11.4.13.1 | Prepare Reclaim Initiation Logic Diagram                    | 359 |

| 11.4.13.2 | Reclaim Time Logic Diagram                                  | 359 |

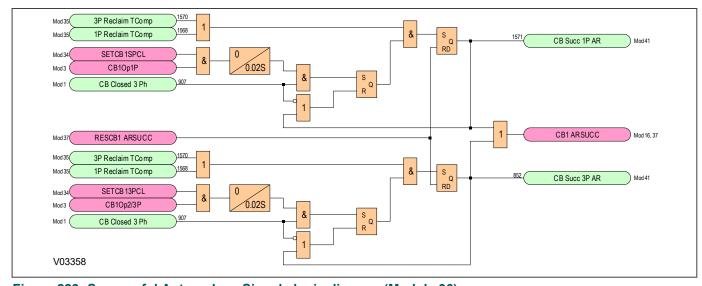

| 11.4.13.3 | Successful Autoreclose Signals Logic Diagram                | 359 |

viii P54-TM-EN-2

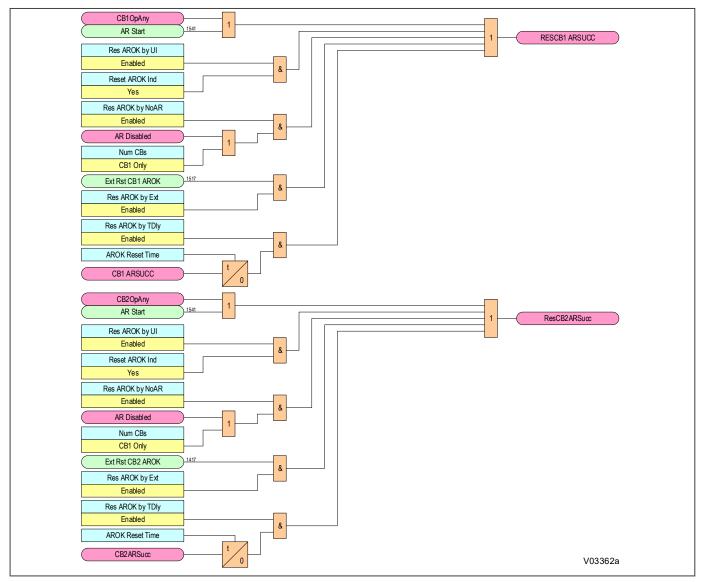

| 11.4.13.4              | Autoreclose Reset Successful Indication Logic Diagram                                    | 360        |

|------------------------|------------------------------------------------------------------------------------------|------------|

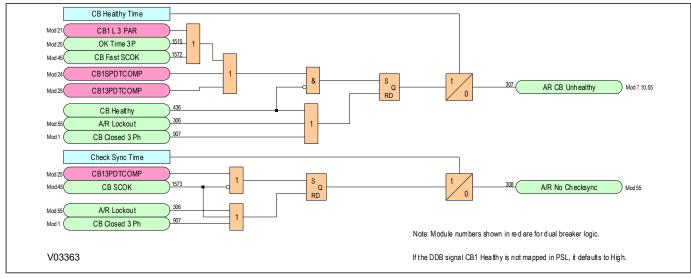

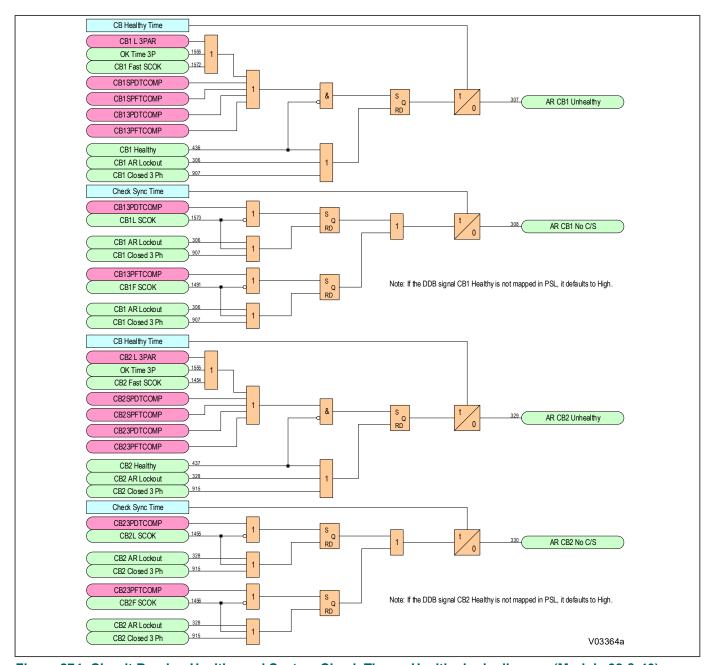

| 11.4.14                | CB Healthy and System Check Timers                                                       | 360        |

| 11.4.14.1              | CB Healthy and System Check Timers Logic Diagram                                         | 361        |

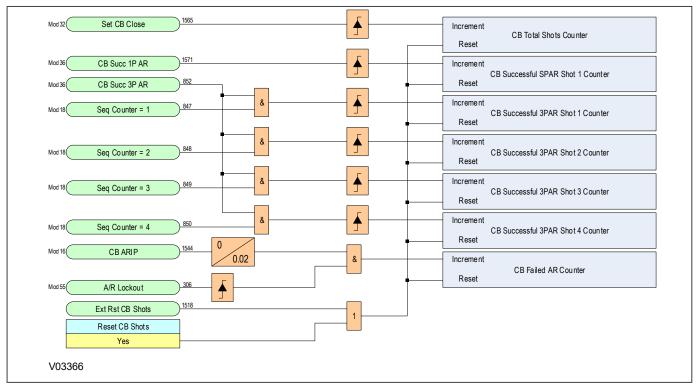

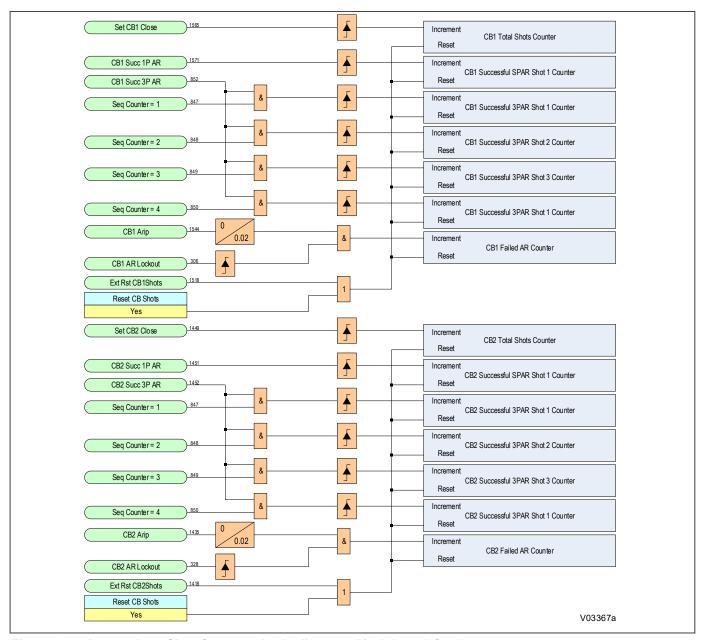

| 11.4.15                | Autoreclose Shot Counters                                                                | 361        |

| 11.4.15.1              | Autoreclose Shot Counters Logic Diagram                                                  | 362        |

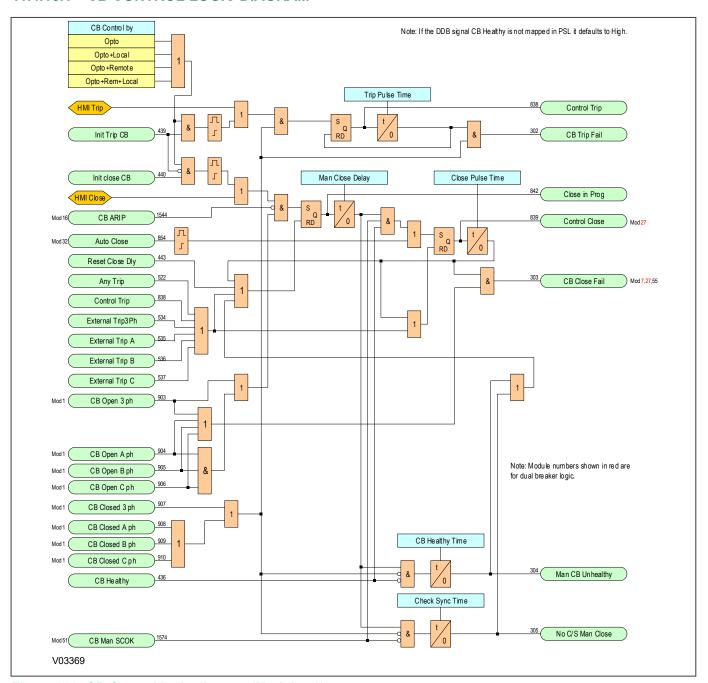

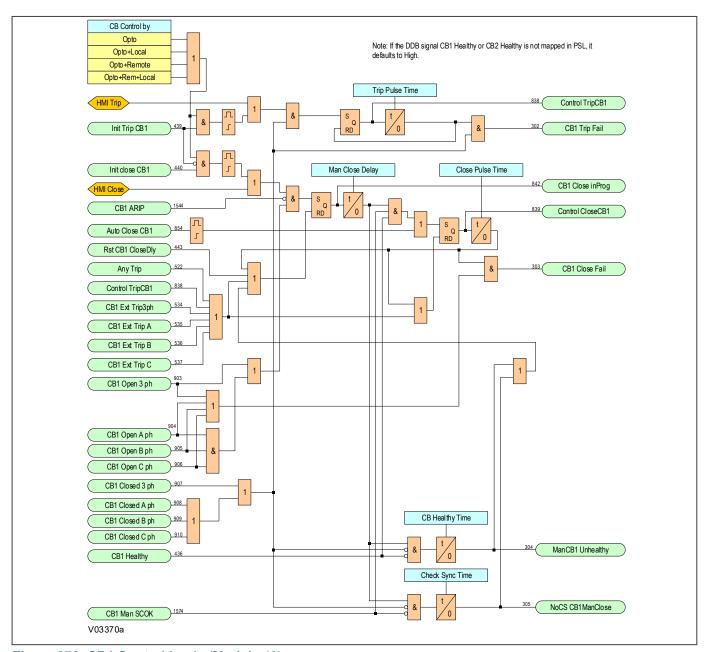

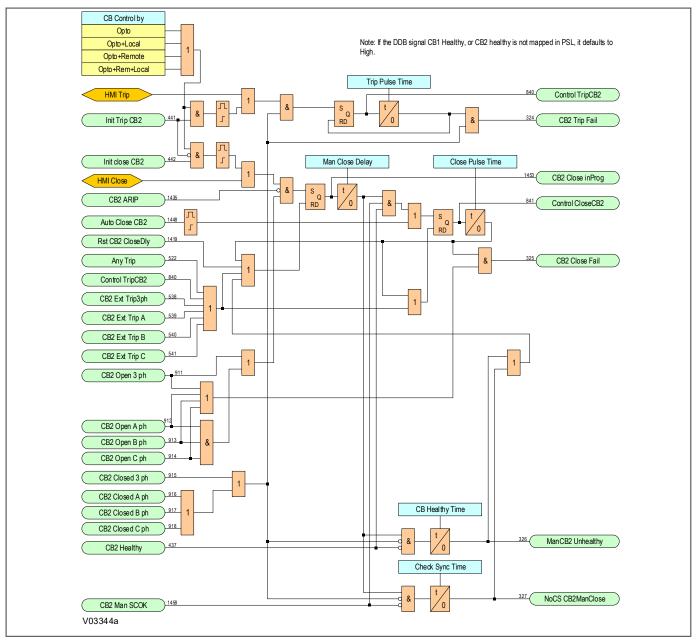

| 11.4.16                | Circuit Breaker Control                                                                  | 363        |

| 11.4.16.1              | CB Control Logic Diagram                                                                 | 363        |

| 11.4.17                | Circuit Breaker Trip Time Monitoring                                                     | 363        |

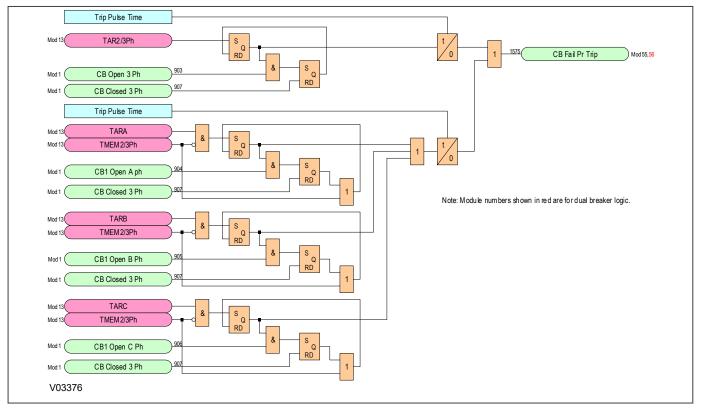

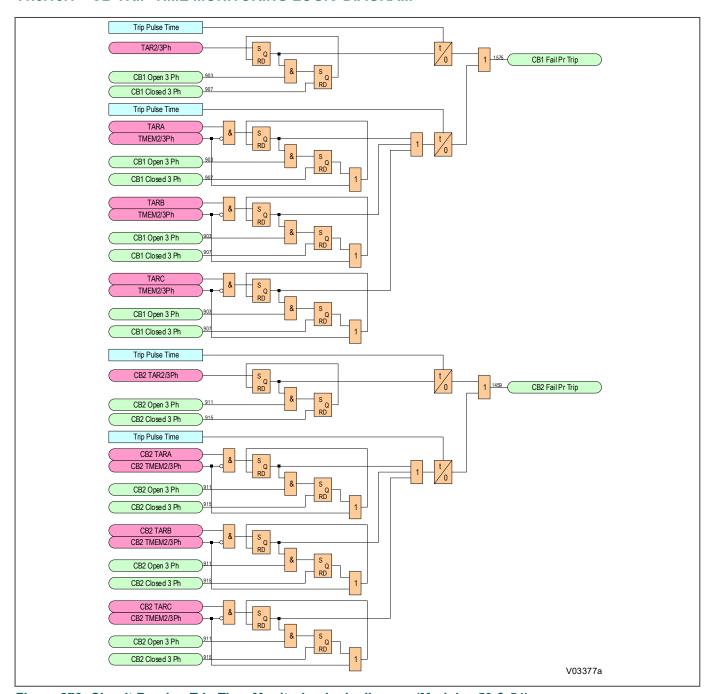

| 11.4.17.1              | CB Trip Time Monitoring Logic Diagram                                                    | 364        |

| 11.4.18                | Autoreclose Lockout                                                                      | 364        |

| 11.4.18.1              | CB Lockout Logic Diagram                                                                 | 365        |

| 11.4.19                | Reset Circuit Breaker Lockout                                                            | 365        |

| 11.4.19.1              | Reset CB Lockout Logic Diagram                                                           | 366        |

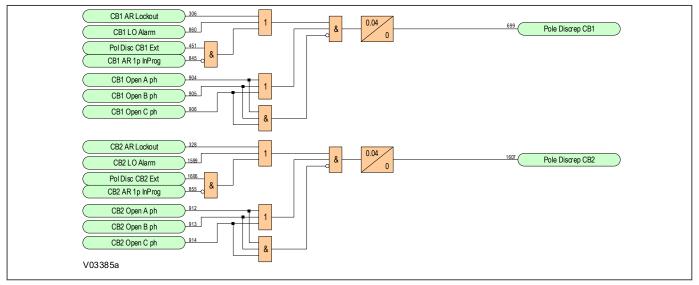

| 11.4.20                | Pole Discrepancy                                                                         | 366        |

| 11.4.20.1              | Pole Discrepancy Logic Diagram                                                           | 367        |

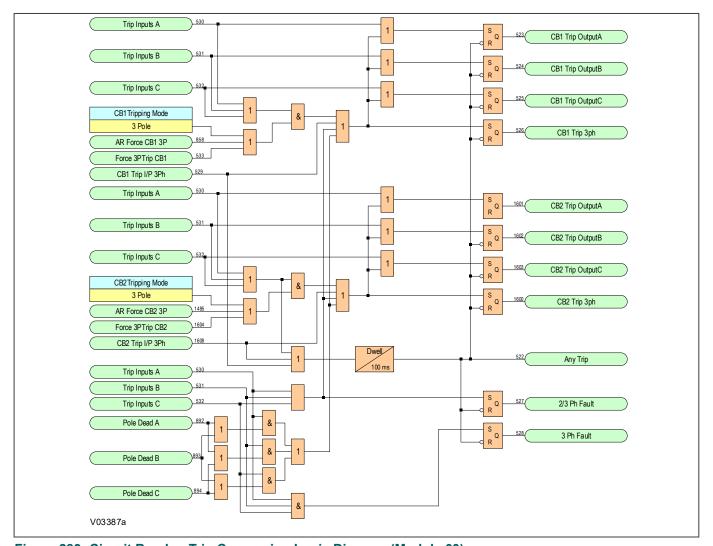

| 11.4.21                | Circuit Breaker Trip Conversion                                                          | 367        |

| 11.4.21.1              | CB Trip Conversion Logic Diagram                                                         | 367        |

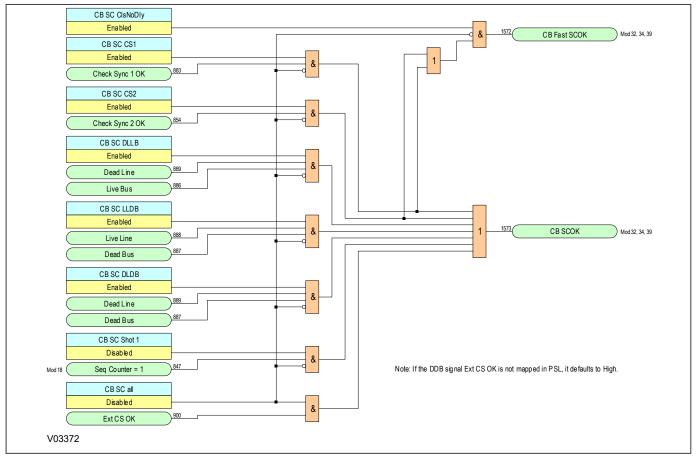

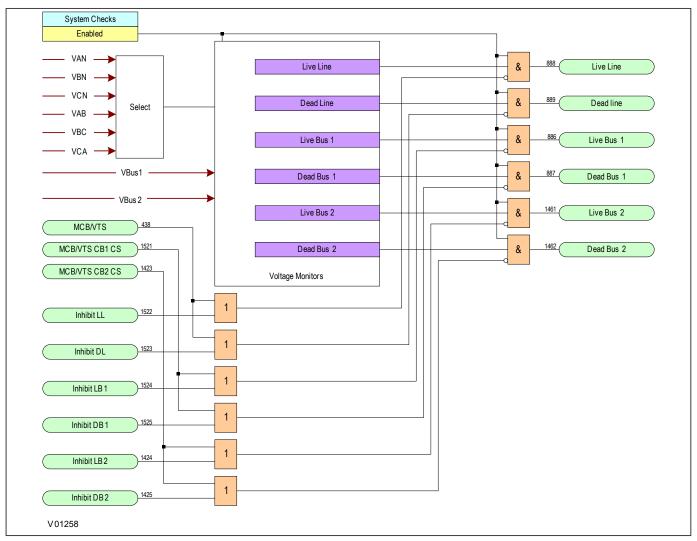

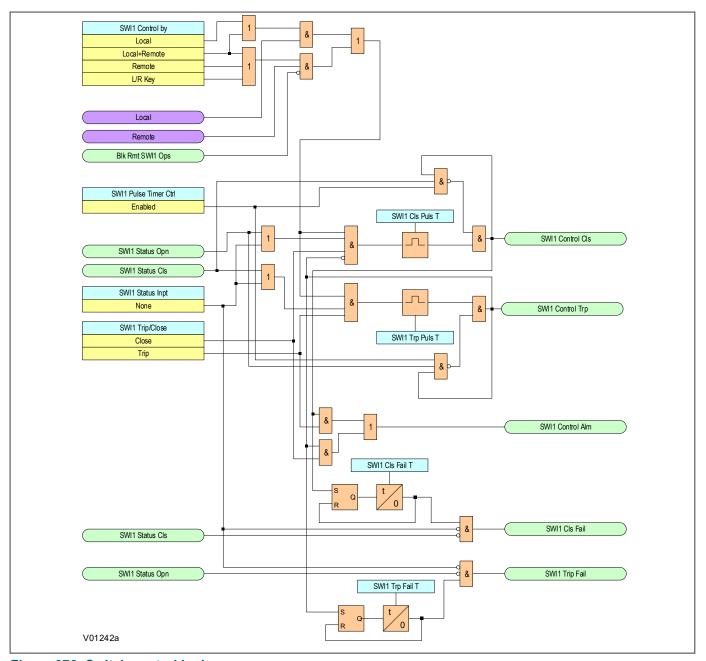

| 11.4.22                | Monitor Checks for CB Closure                                                            | 367        |

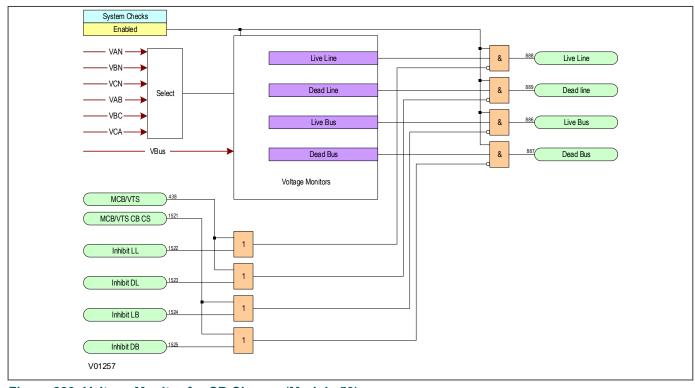

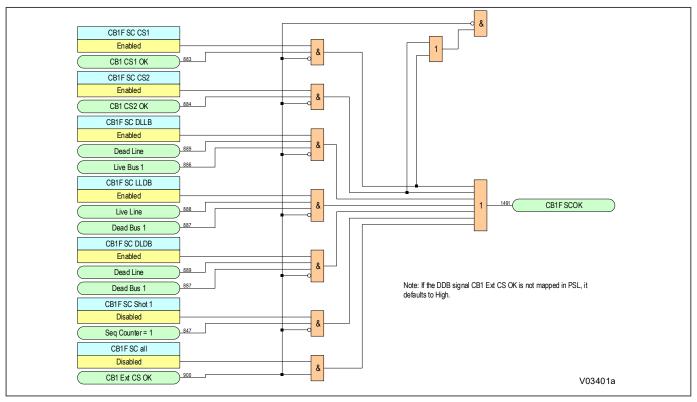

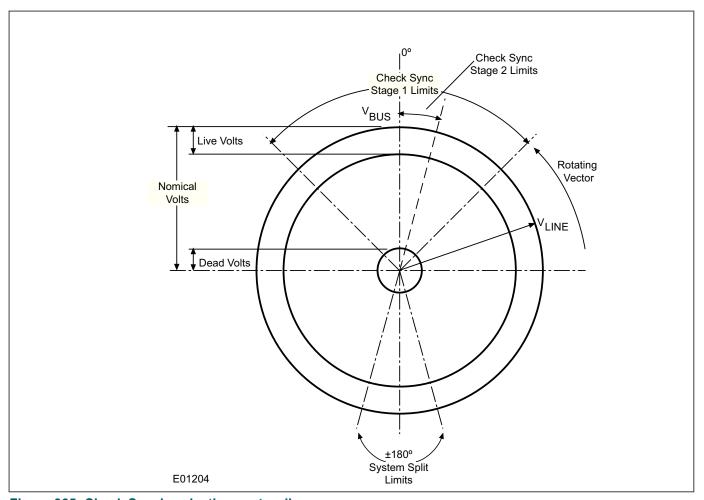

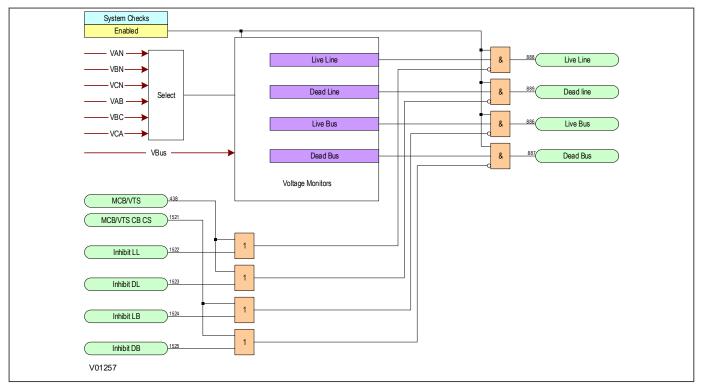

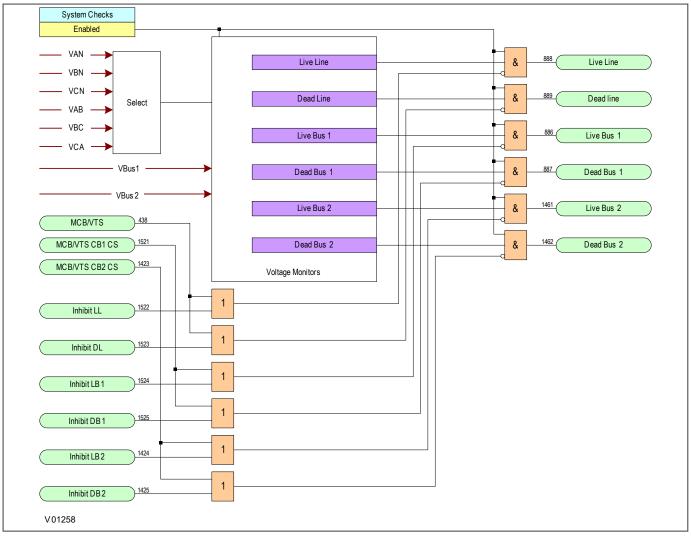

| 11.4.22.1<br>11.4.22.2 | Voltage Monitor for CB Closure                                                           | 368        |

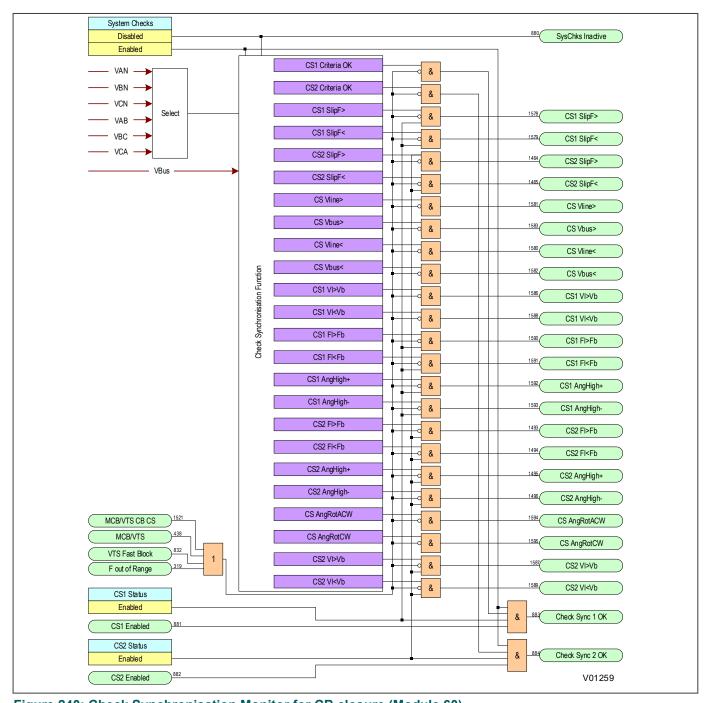

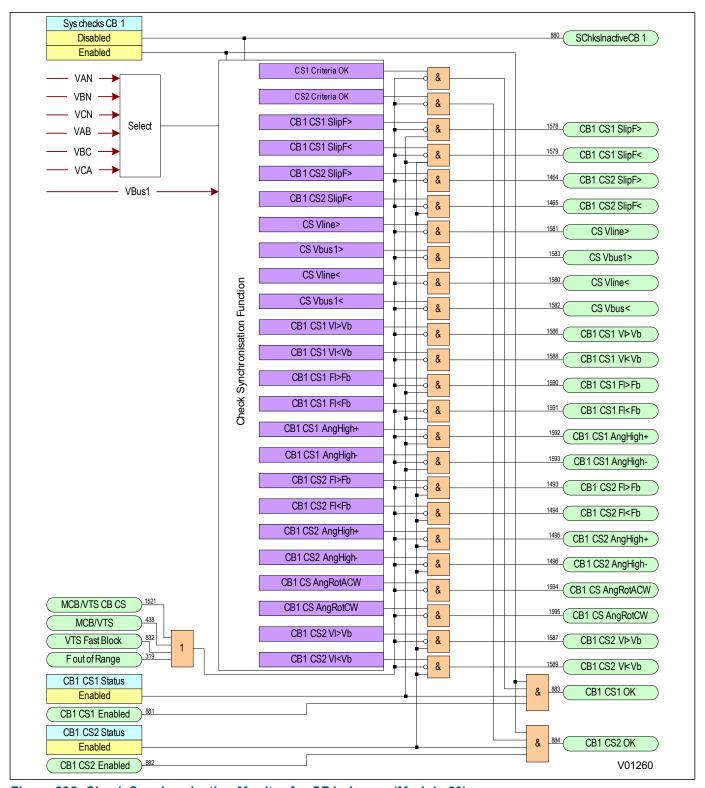

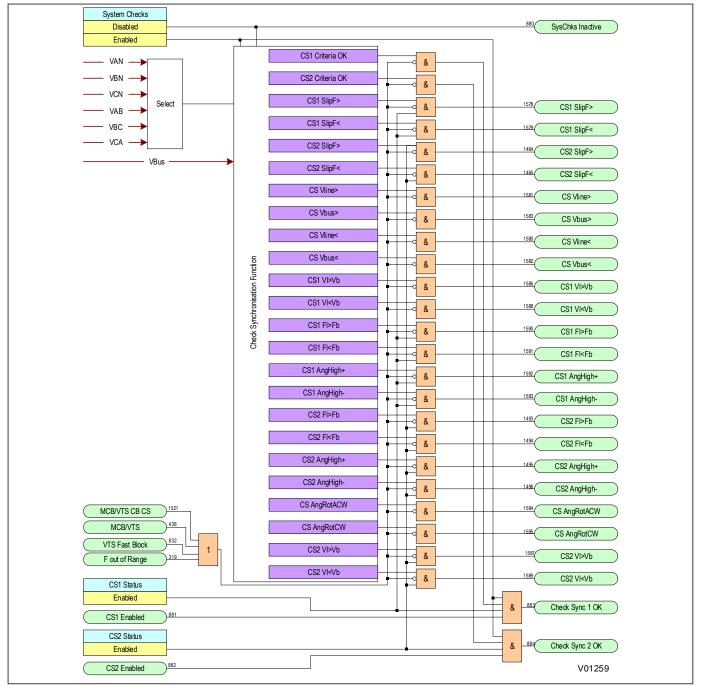

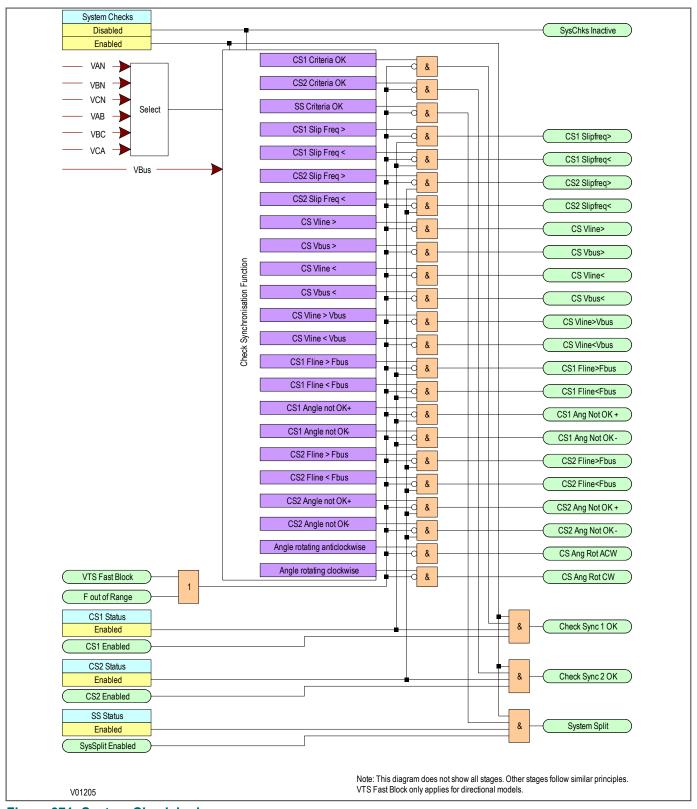

| 11.4.22.2              | Check Synchronisation Monitor for CB Closure                                             | 369        |

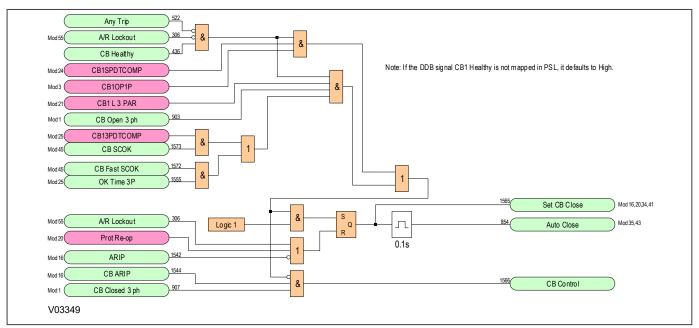

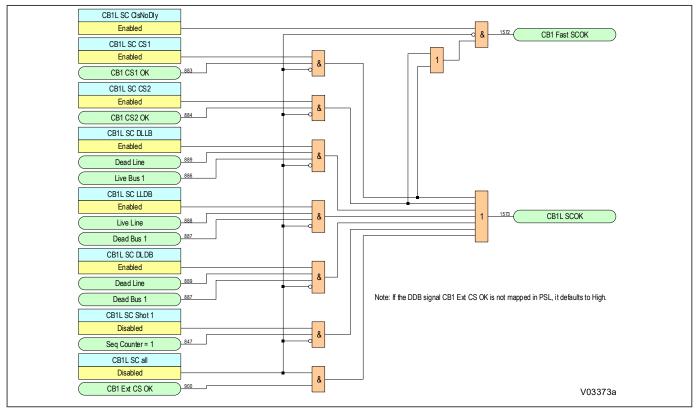

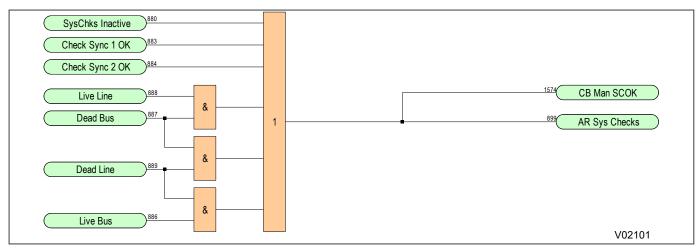

| 11.4.23                | Synchronisation Checks for CB Closure Three-phase Autoreclose System Check Logic Diagram | 369<br>371 |

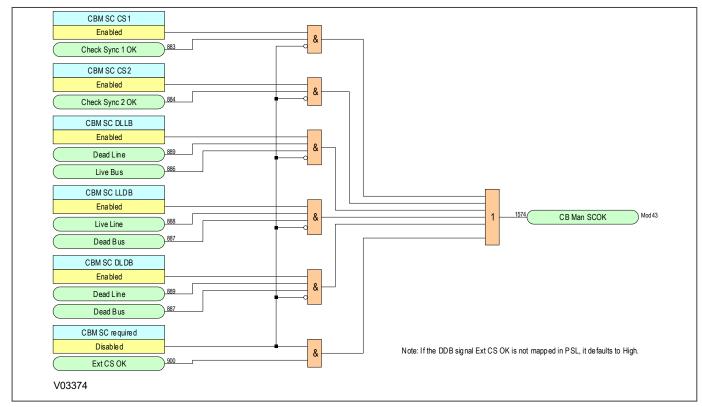

| 11.4.23.1              | CB Manual Close System Check Logic Diagram                                               | 371        |

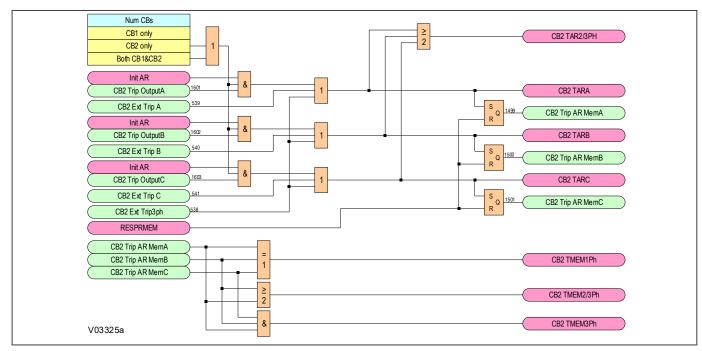

| 11.5                   | Logic Modules (Dual CB)                                                                  | 373        |

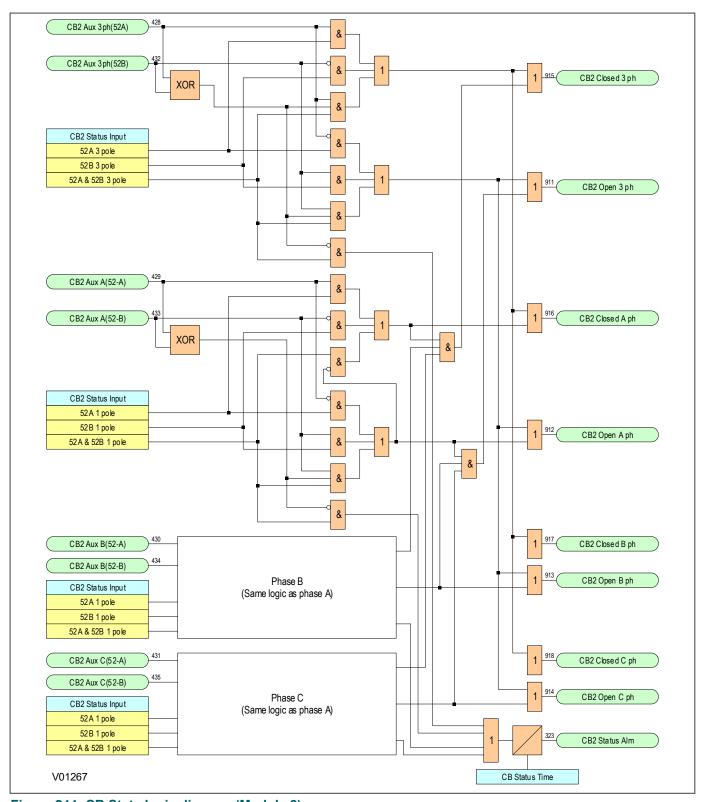

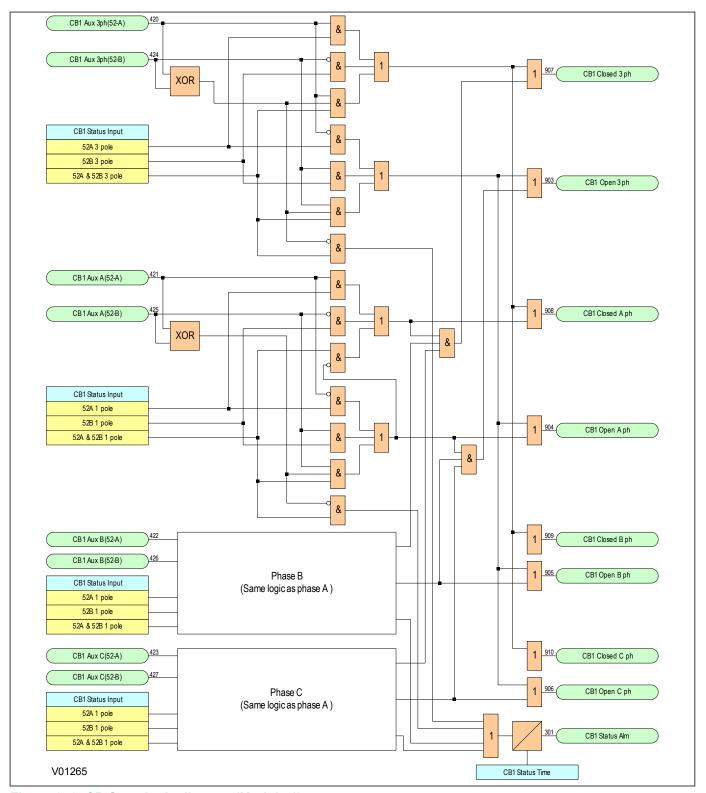

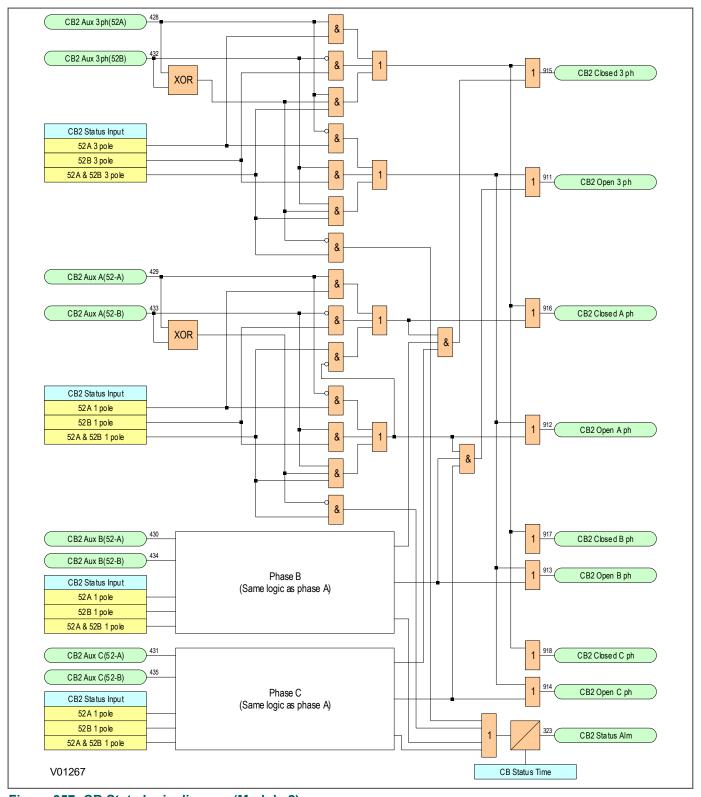

| 11.5.1                 | Circuit Breaker Status Monitor                                                           | 373        |

| 11.5.1.1               | CB State Monitor                                                                         | 374        |

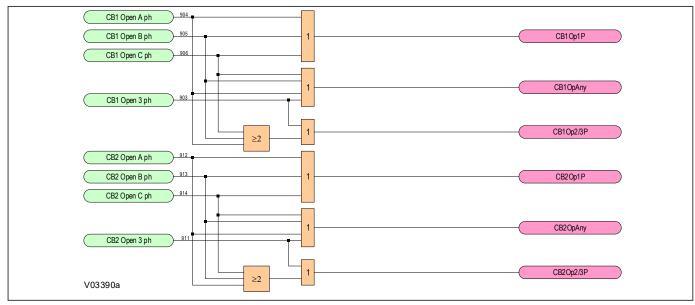

| 11.5.2                 | Circuit Breaker Open Logic                                                               | 375        |

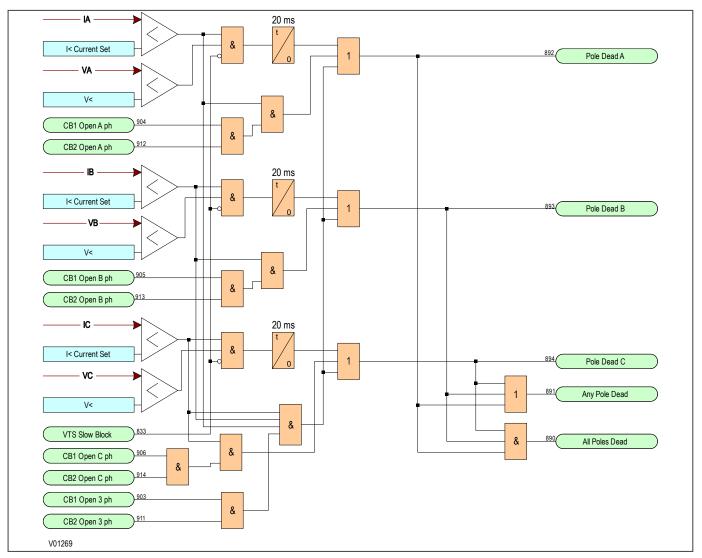

| 11.5.2.1               | Circuit Breaker Open Logic Diagram                                                       | 376        |

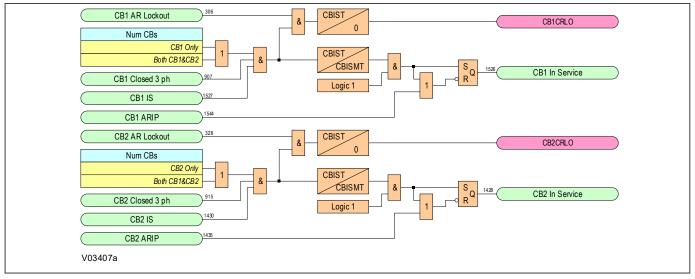

| 11.5.3                 | Circuit Breaker in Service Logic                                                         | 376        |

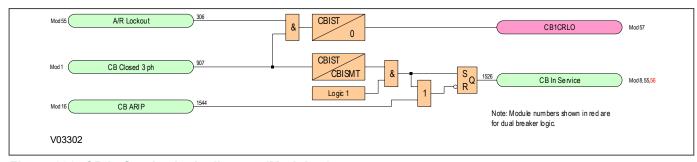

| 11.5.3.1               | Circuit Breaker in Service Logic Diagram                                                 | 377        |

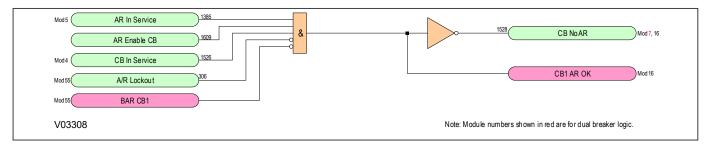

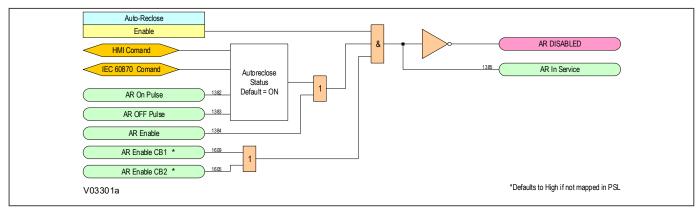

| 11.5.4                 | Autoreclose Enable Logic                                                                 | 377        |

| 11.5.4.1               | Autoreclose Enable Logic Diagram                                                         | 377        |

| 11.5.5                 | Autoreclose Leader/Follower                                                              | 377        |

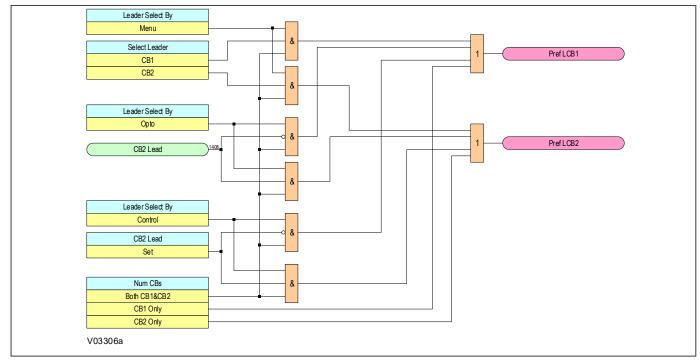

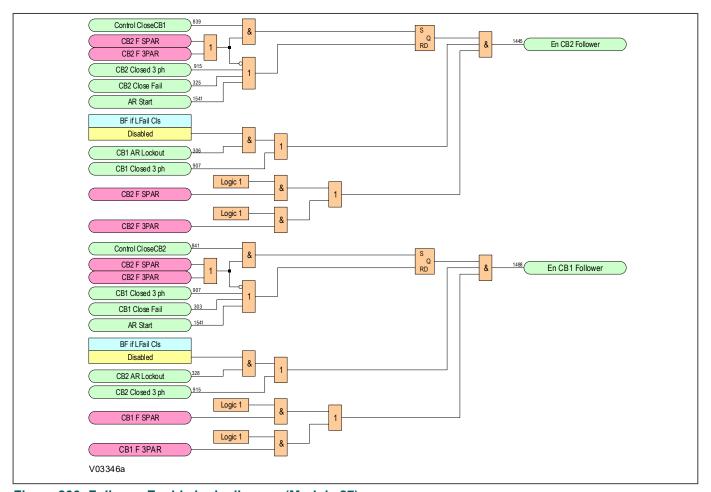

| 11.5.5.1               | Leader/Follower CB Selection Logic Diagram                                               | 378        |

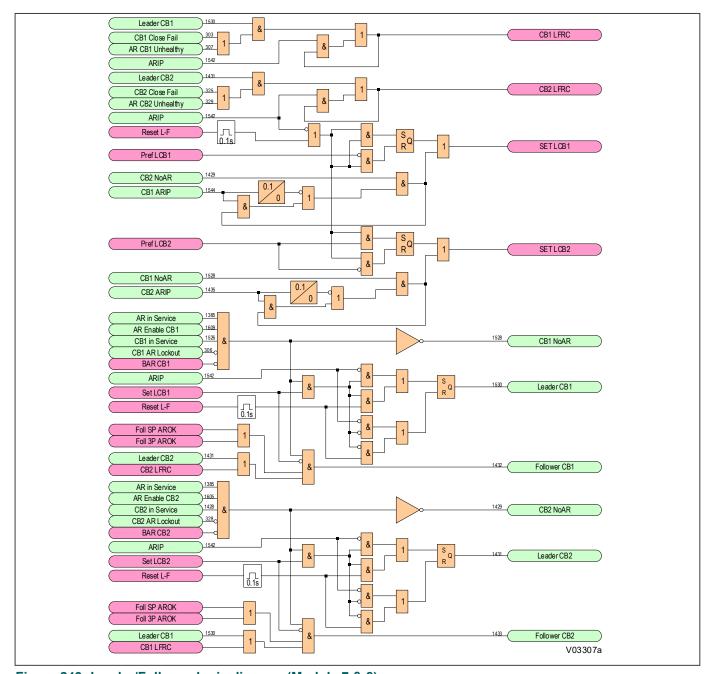

| 11.5.5.2               | Leader Follower Logic Diagram                                                            | 379        |

| 11.5.6                 | Autoreclose Modes                                                                        | 379        |

| 11.5.6.1               | Single-Phase and Three-Phase Autoreclose                                                 | 380        |

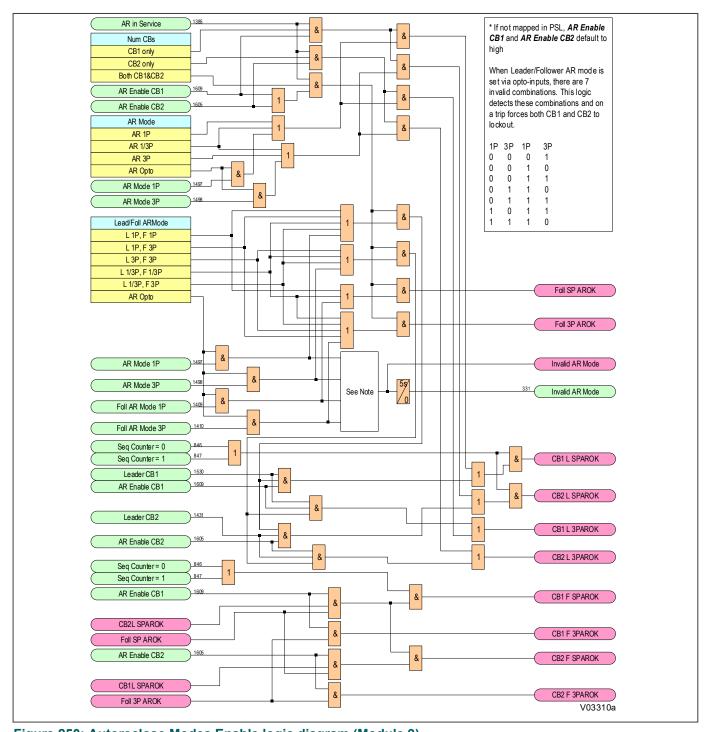

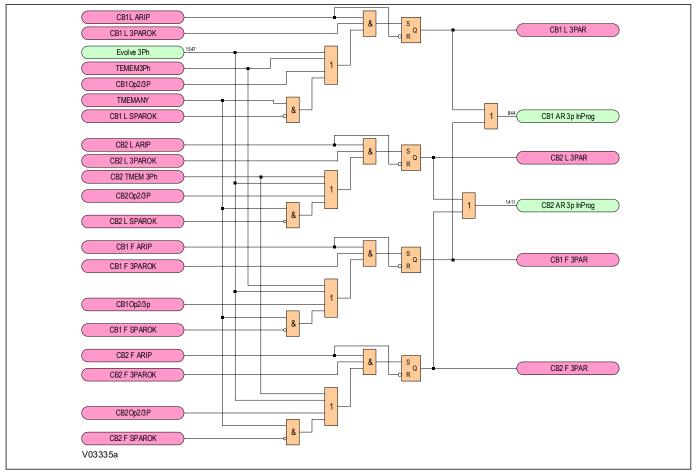

| 11.5.6.2               | Autoreclose Modes Enable Logic Diagram                                                   | 381        |

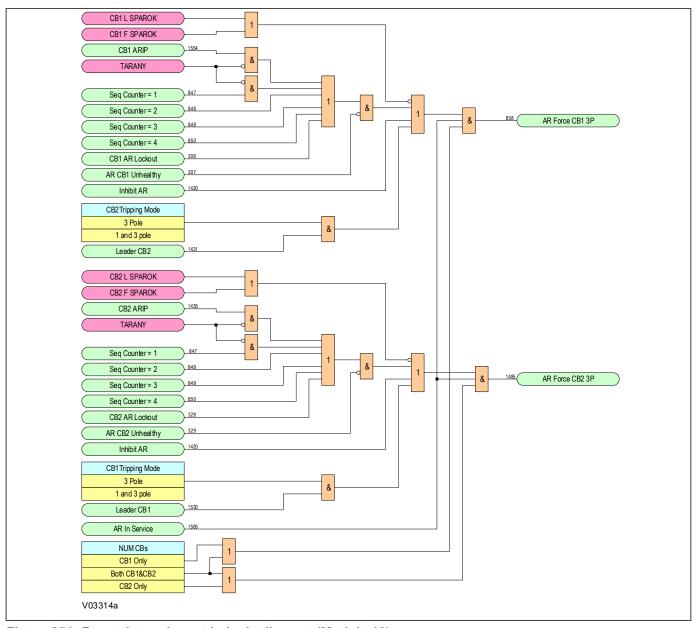

| 11.5.7                 | AR Force Three-Phase Trip Logic                                                          | 381        |

| 11.5.7.1               | Force Three-Phase Trip Logic Diagram                                                     | 382        |

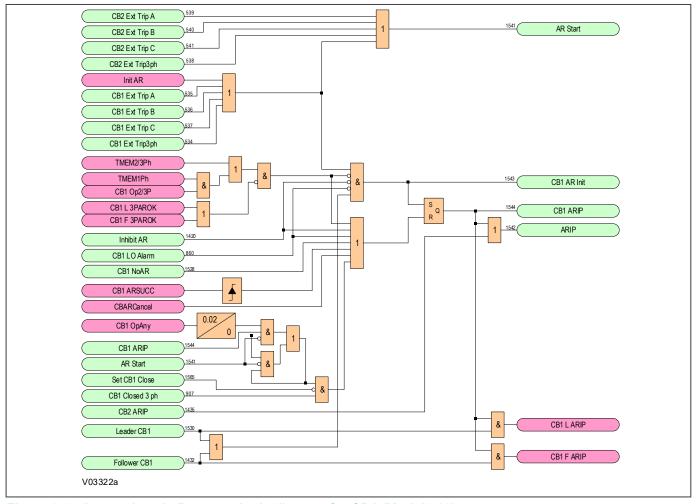

| 11.5.8                 | Autoreclose Initiation Logic                                                             | 382        |

| 11.5.8.1               | Autoreclose Initiation Logic Diagram                                                     | 383        |

| 11.5.8.2               | Autoreclose Trip Test Logic Diagram                                                      | 384        |

| 11.5.8.3               | External Trip Logic Diagram for CB1                                                      | 385        |

| 11.5.8.4               | External Trip Logic Diagram for CB2                                                      | 386        |

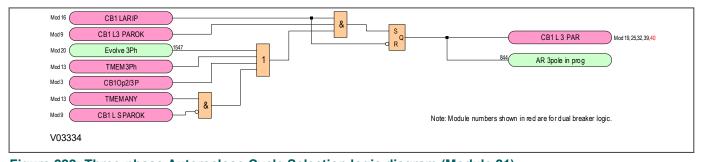

| 11.5.8.5               | Protection Reoperation and Evolving Fault Logic Diagram                                  | 387        |

| 11.5.8.6               | Fault Memory Logic Diagram                                                               | 387        |

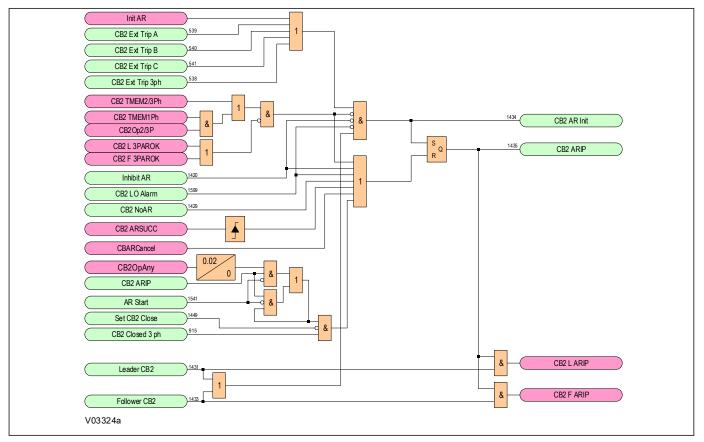

| 11.5.9                 | Autoreclose In Progress                                                                  | 387        |

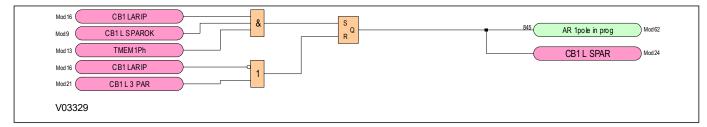

| 11.5.9.1               | Autoreclose In Progress Logic Diagram for CB1                                            | 388        |

| 11.5.9.2               | Autoreclose In Progress Logic Diagram for CB2                                            | 389        |

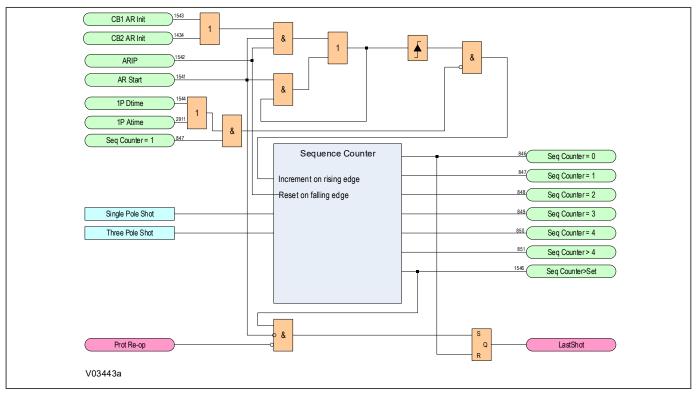

| 11.5.10                | Sequence Counter                                                                         | 389        |

| 11.5.10.1<br>11.5.11   | Autoreclose Sequence Counter Logic Diagram                                               | 390<br>390 |

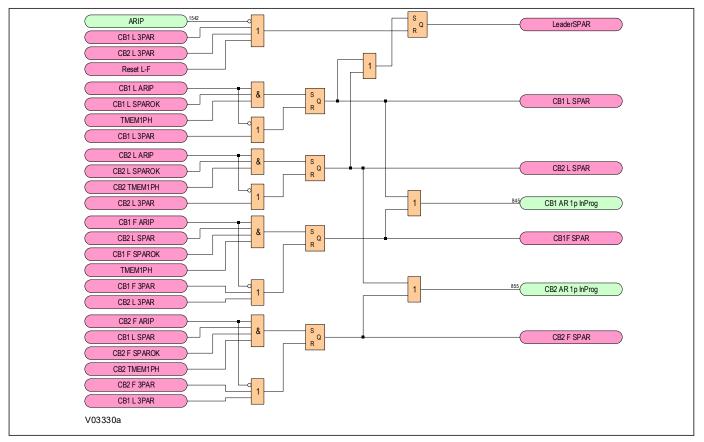

| 11.5.11                | Autoreclose Cycle Selection Single Phase Autoreclose Cycle Selection Logic Diagram       | 390        |

| 11.5.11.1              | 3-phase Autoreclose Cycle Selection                                                      | 392        |

| 11.5.11.2              | Dead Time Control                                                                        | 392        |

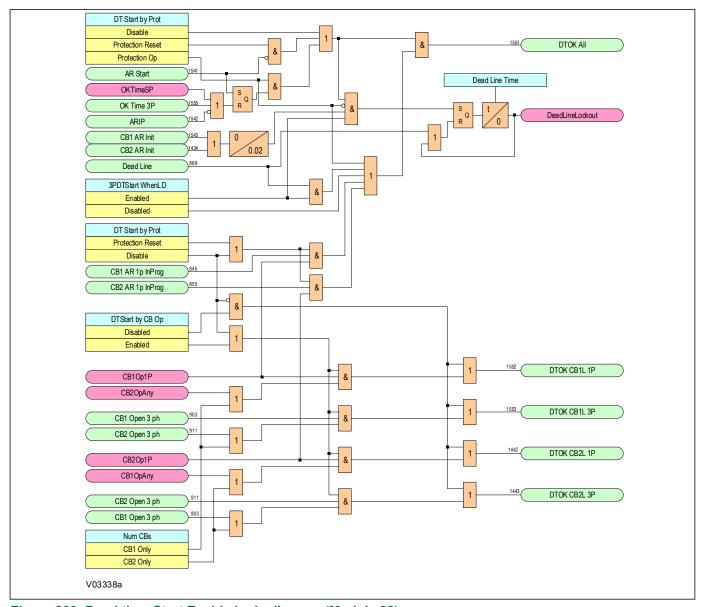

| 11.5.12.1              | Dead Time Start Enable Logic Diagram                                                     | 393        |

| 11.5.12.2              | Single-phase Dead Time and Adaptive Autoreclose (AAR) Lo                                 |            |

|                        | 5 F =                                                                                    |            |

P54-TM-EN-2 ix

| Contents | P54 |

|----------|-----|

| Contents | F34 |

|          |     |

| 11.5.12.3            | Single-phase Leader Dead Time Logic Diagram                                | 395        |

|----------------------|----------------------------------------------------------------------------|------------|

| 11.5.12.4            | 3-phase Leader Dead Time Logic Diagram                                     | 396        |

| 11.5.12.5            | Follower Enable Logic Diagram                                              | 397        |

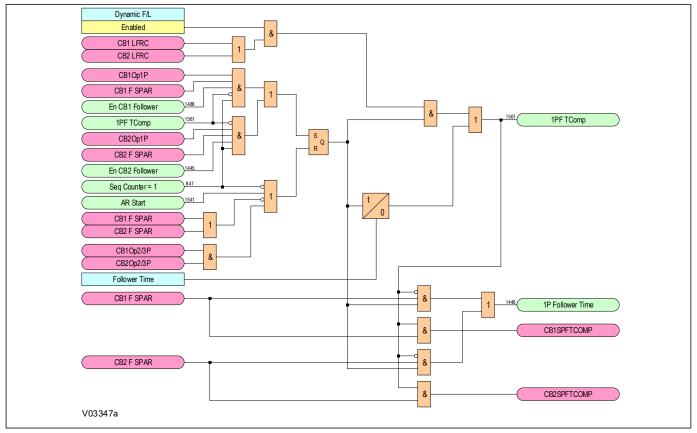

| 11.5.12.6            | Single-phase Follower Timing Logic Diagram                                 | 398        |

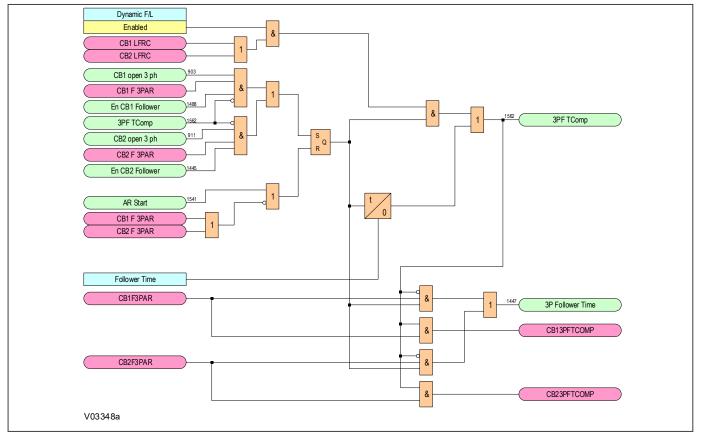

| 11.5.12.7            | Three-phase Follower Timing Logic Diagram                                  | 399        |

| 11.5.13              | Circuit Breaker Autoclose                                                  | 399        |

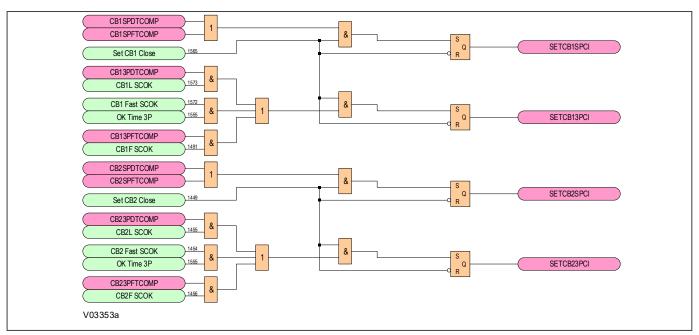

| 11.5.13.1            | Circuit Breaker Autoclose Logic Diagram                                    | 400        |

| 11.5.14              | Reclaim Time                                                               | 400        |

| 11.5.14.1            | Prepare Reclaim Initiation Logic Diagram                                   | 401        |

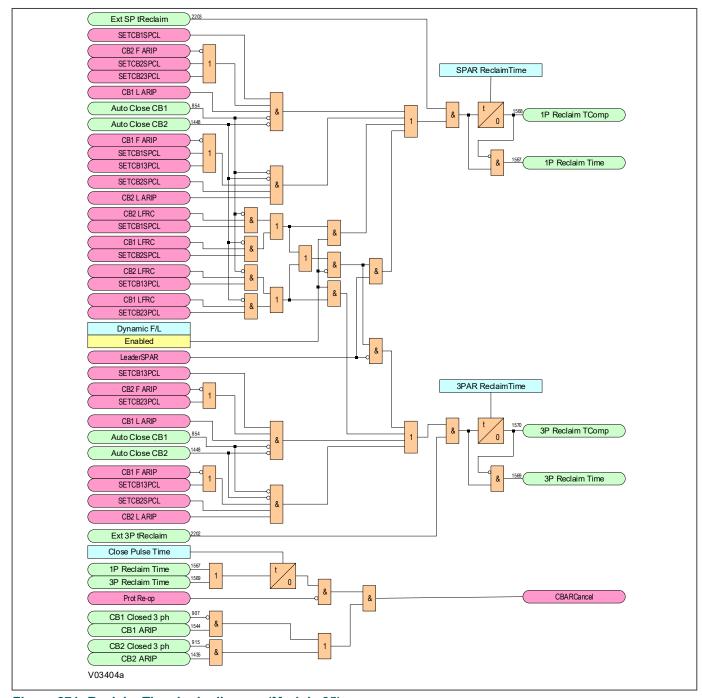

| 11.5.14.2            | Reclaim Time Logic Diagram                                                 | 402        |

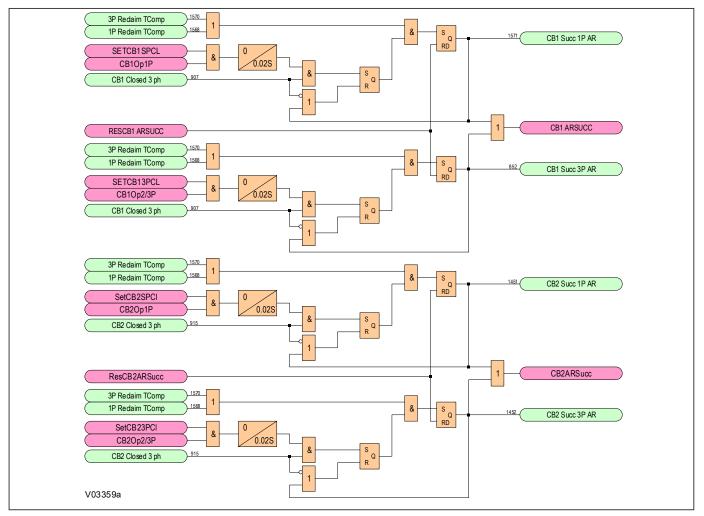

| 11.5.14.3            | Successful Autoreclose Signals Logic Diagram                               | 403        |

| 11.5.14.4            | Autoreclose Reset Successful Indication Logic Diagram                      | 404        |

| 11.5.15<br>11.5.15.1 | CB Healthy and System Check Timers                                         | 404        |

| 11.5.15.1            | CB Healthy and System Check Timers Logic Diagram Autoreclose Shot Counters | 405<br>405 |

| 11.5.16.1            | Autoreclose Shot Counters Autoreclose Shot Counters Logic Diagram          | 406        |

| 11.5.10.1            | Circuit Breaker Control                                                    | 407        |

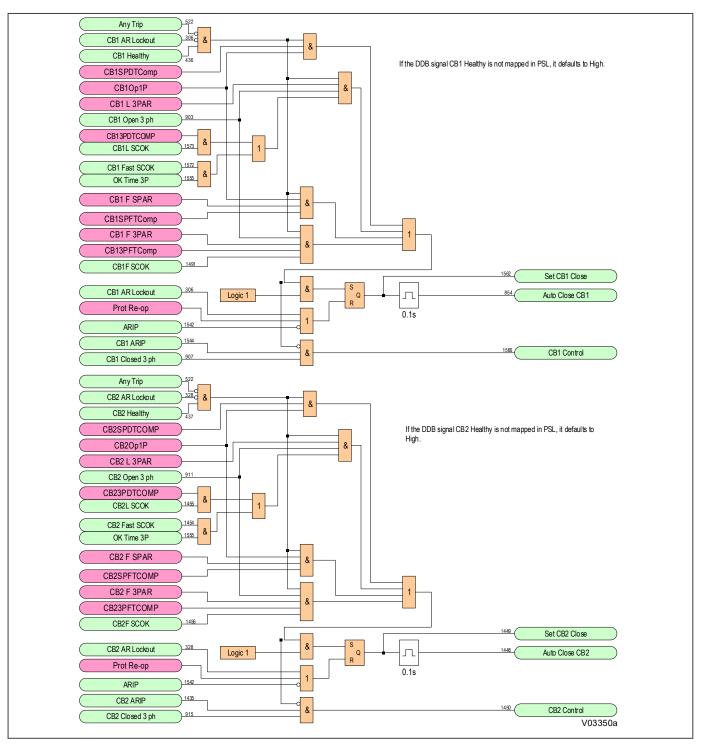

| 11.5.17              | CB Control Logic Diagram                                                   | 407        |

| 11.5.17.1            | Circuit Breaker Trip Time Monitoring                                       | 408        |

| 11.5.18.1            | CB Trip Time Monitoring Logic Diagram                                      | 400        |

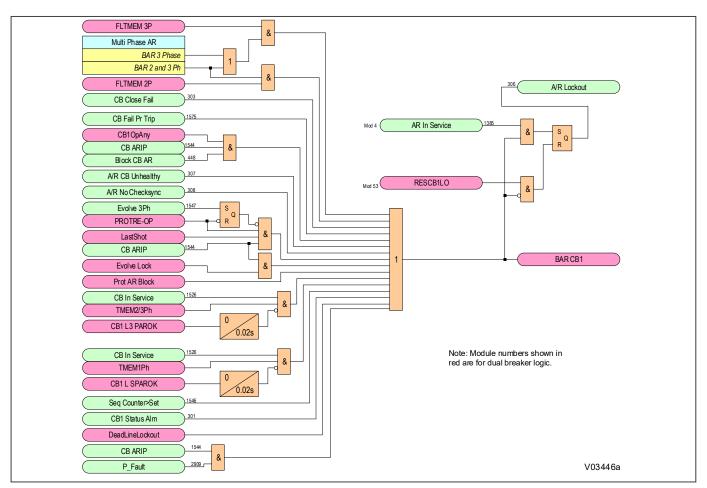

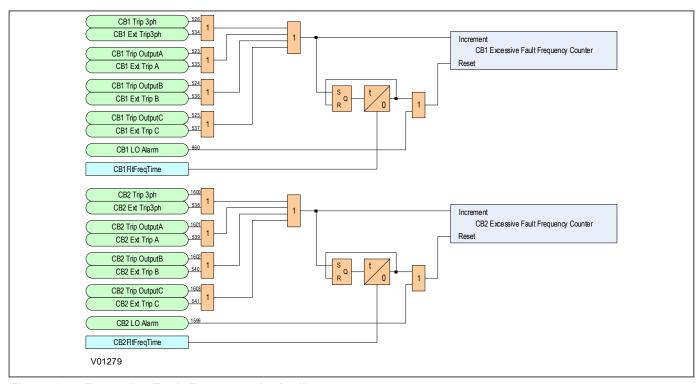

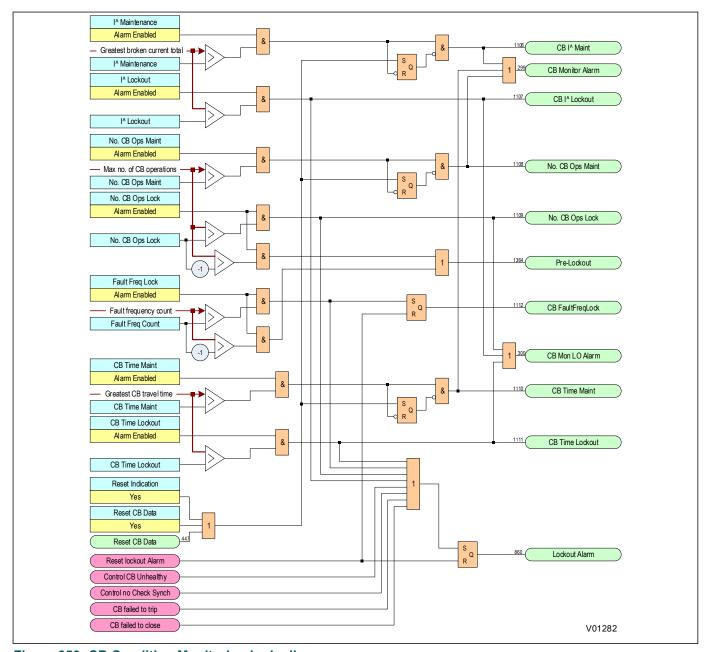

| 11.5.10.1            | Autoreclose Lockout                                                        | 409        |

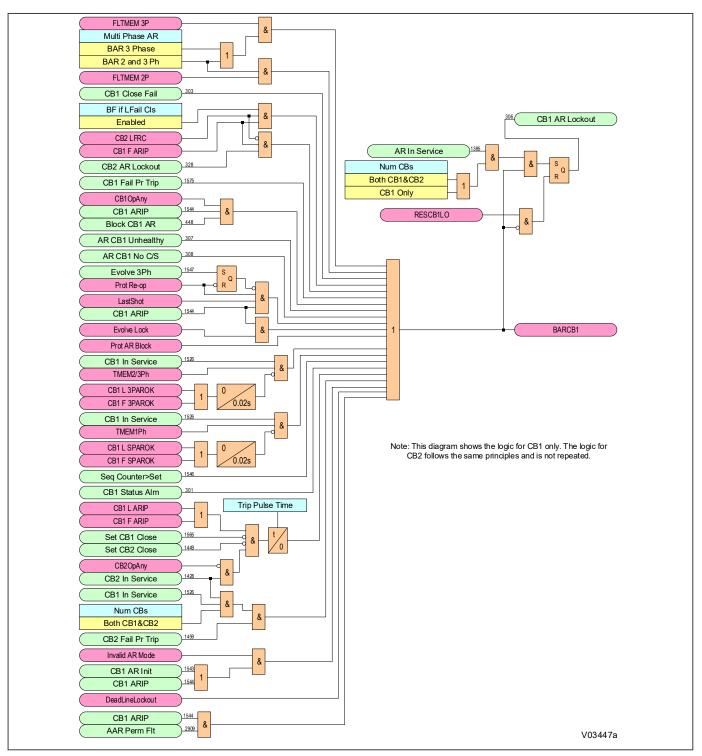

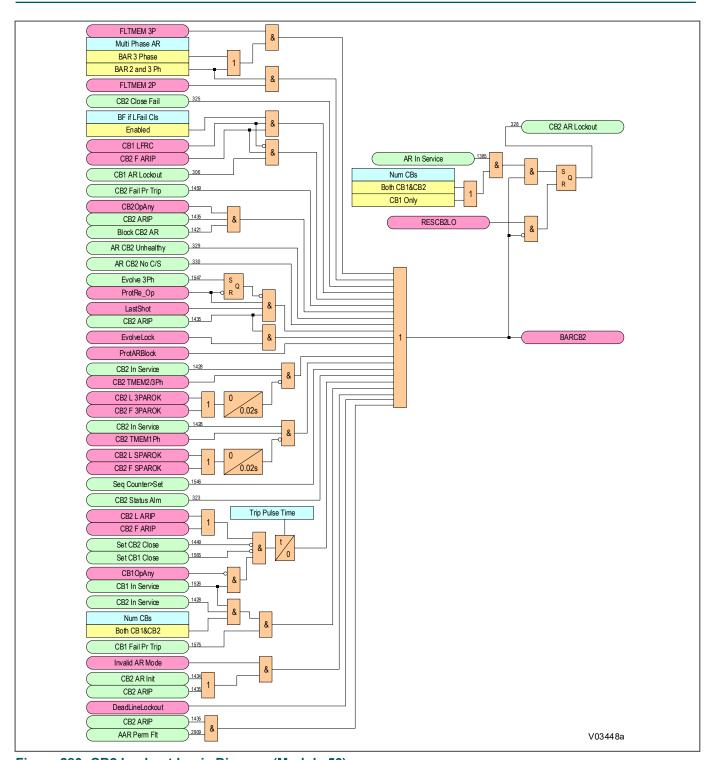

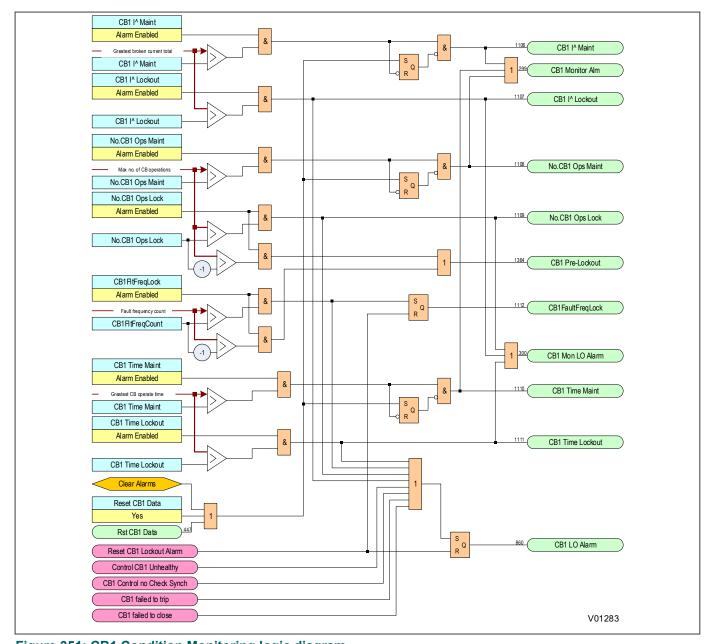

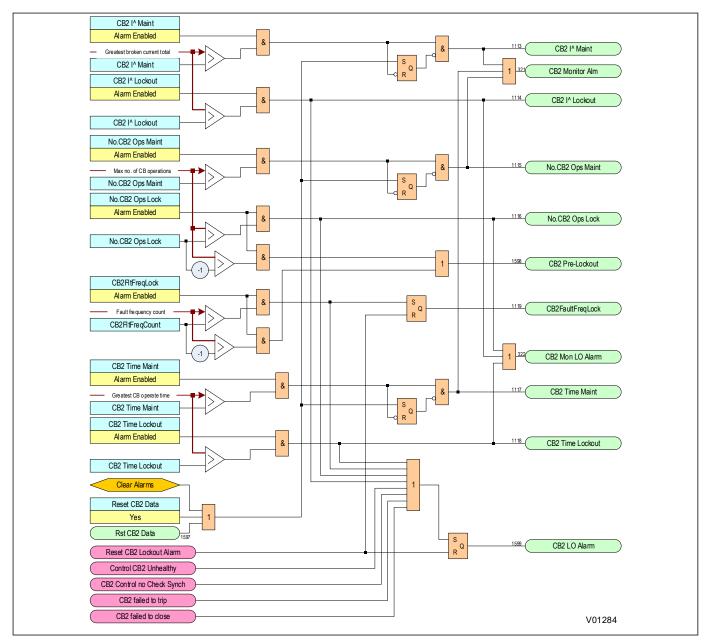

| 11.5.19.1            | CB Lockout Logic Diagram                                                   | 411        |

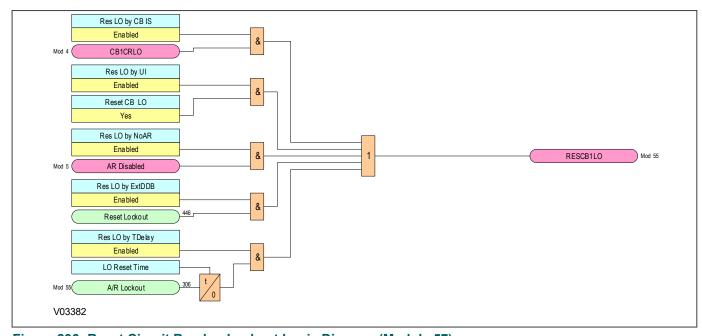

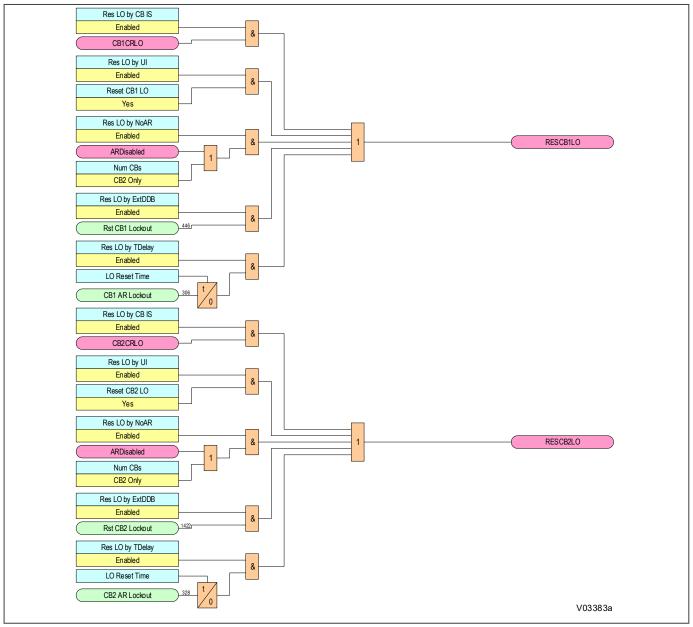

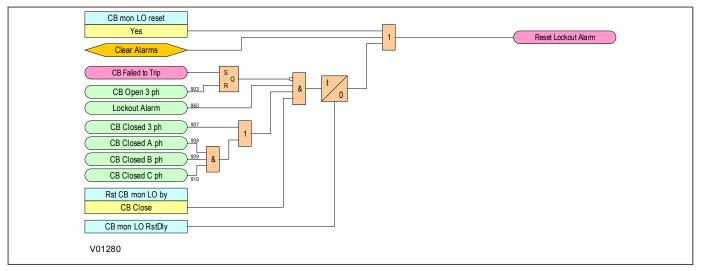

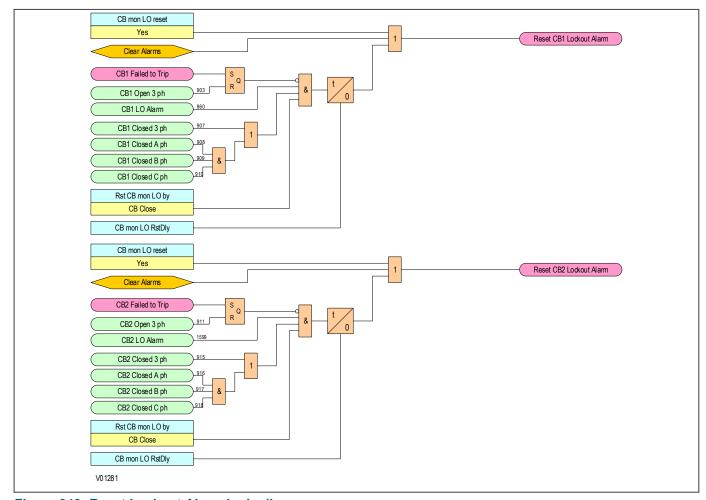

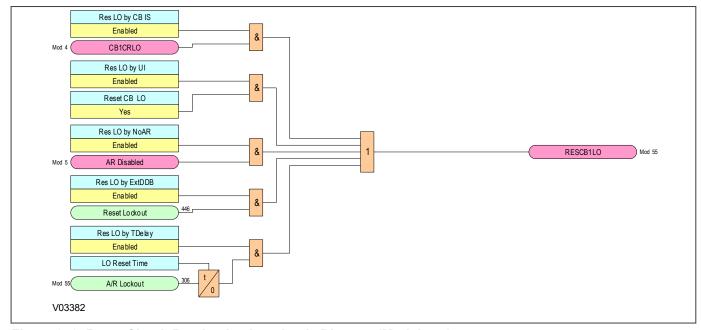

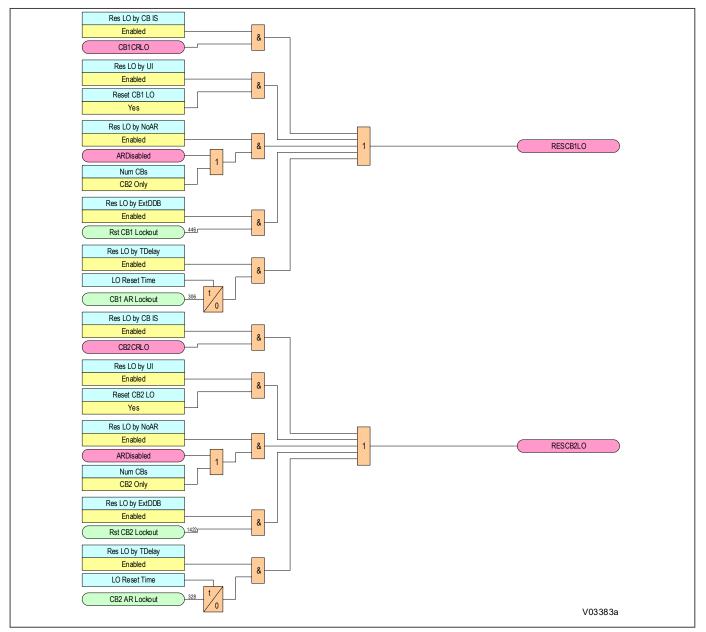

| 11.5.20              | Reset Circuit Breaker Lockout                                              | 412        |

| 11.5.20.1            | Reset CB Lockout Logic Diagram                                             | 414        |

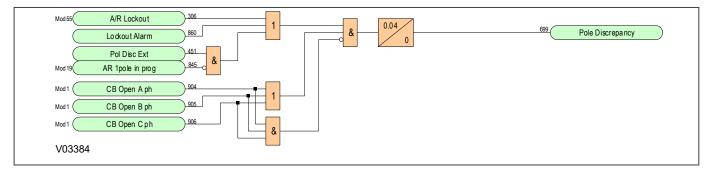

| 11.5.21              | Pole Discrepancy                                                           | 414        |

| 11.5.21.1            | Pole Discrepancy Logic Diagram                                             | 415        |

| 11.5.22              | Circuit Breaker Trip Conversion                                            | 415        |

| 11.5.22.1            | CB Trip Conversion Logic Diagram                                           | 416        |

| 11.5.23              | Monitor Checks for CB Closure                                              | 416        |

| 11.5.23.1            | Voltage Monitor for CB Closure                                             | 417        |

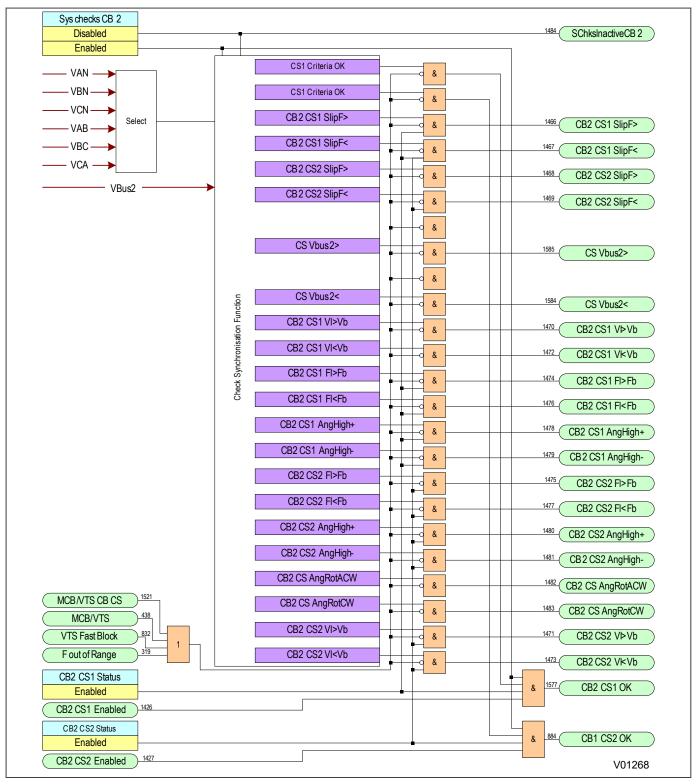

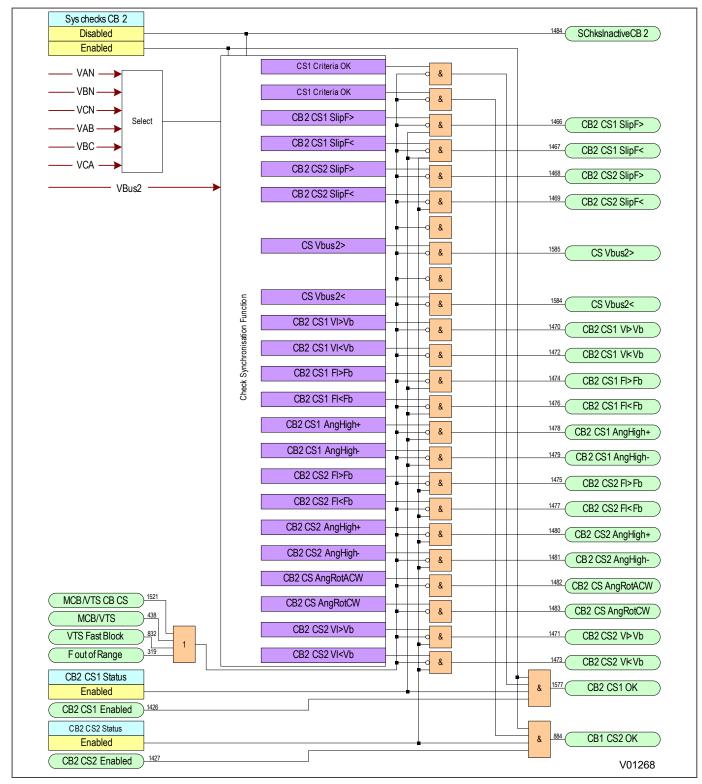

| 11.5.23.2            | Check Synchronisation Monitor for CB Closure                               | 418        |

| 11.5.24              | Synchronisation Checks for CB Closure                                      | 419        |

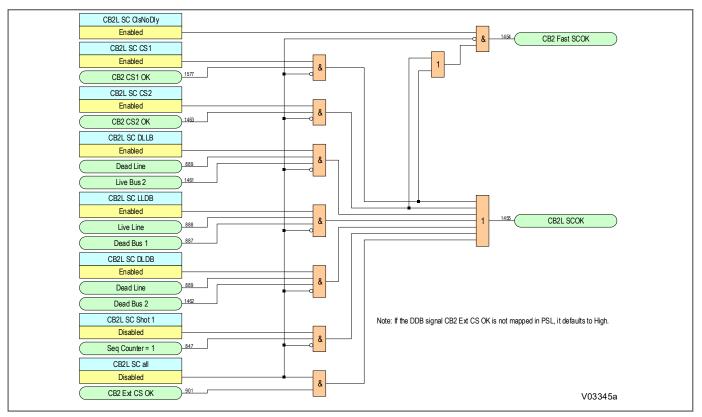

| 11.5.24.1            | Three-phase Autoreclose Leader Check Logic Diagram                         | 421        |

| 11.5.24.2            | Three-phase Autoreclose Follower Check Logic Diagram                       | 422        |

| 11.5.24.3            | CB Manual Close System Check Logic Diagram                                 | 423        |

| 11.6                 | Setting Guidelines                                                         | 424        |

| 11.6.1               | De-ionising Time Guidance                                                  | 424        |

| 11.6.2               | Dead Timer Setting Guidelines                                              | 424        |

| 11.6.2.1             | Example Dead Time Calculation                                              | 425        |

| 11.6.3               | Reclaim Time Setting Guidelines                                            | 425        |

| 11.6.4               | Autoreclose Shot Counters                                                  | 425        |

|                      |                                                                            |            |

| Chapte               | r 12 CB Fail Protection                                                    | 427        |

| 12.1                 | Chapter Overview                                                           | 428        |

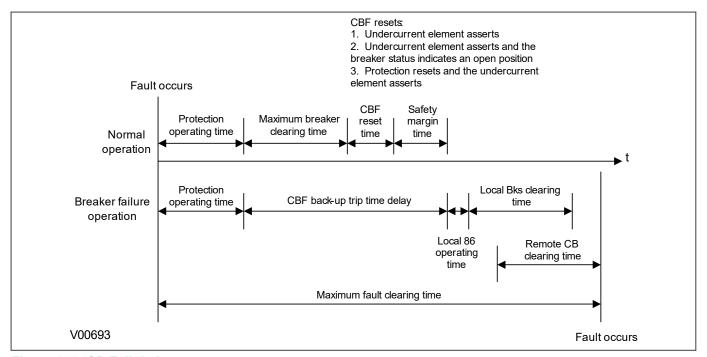

| 12.2                 | Circuit Breaker Fail Protection                                            | 429        |

| 12.3                 | Circuit Breaker Fail Implementation                                        | 430        |

| 12.3.1               | Circuit Breaker Fail Timers                                                | 430        |

| 12.3.2               | Circuit Breaker Fail Initiation                                            | 430        |

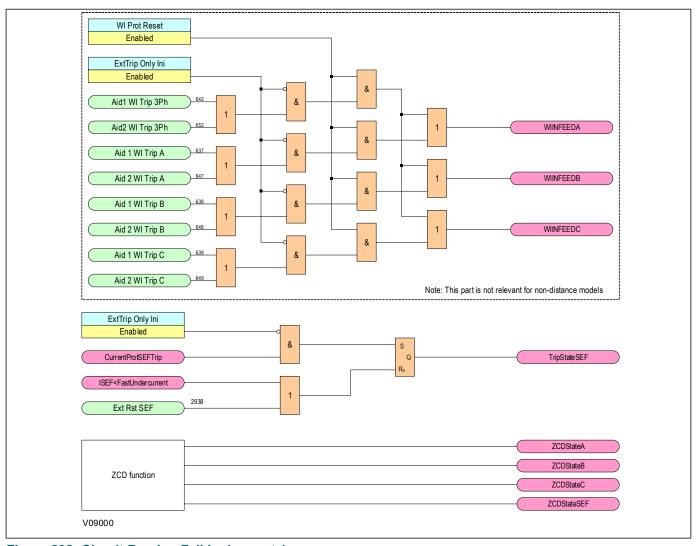

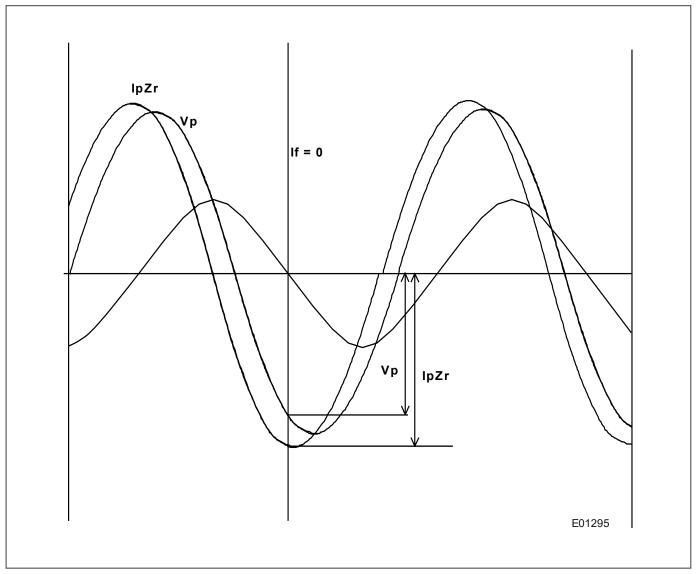

| 12.3.3               | Zero Crossing Detection                                                    | 431        |

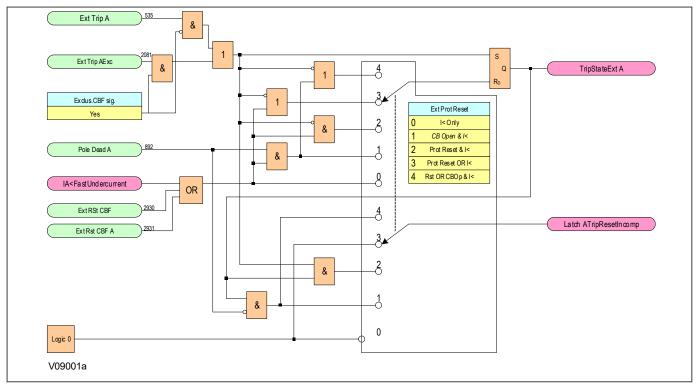

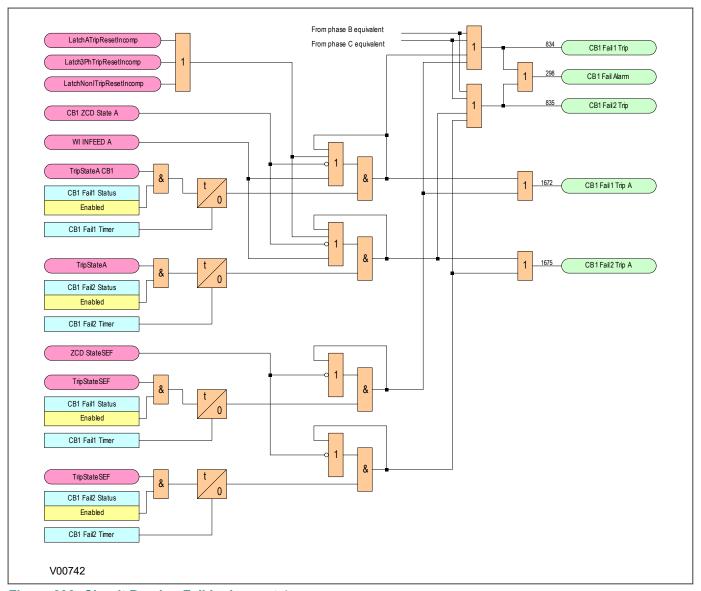

| 12.4                 | Circuit Breaker Fail Logic                                                 | 432        |

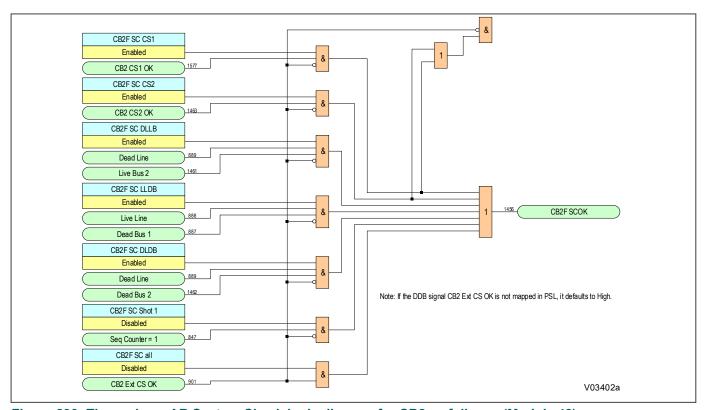

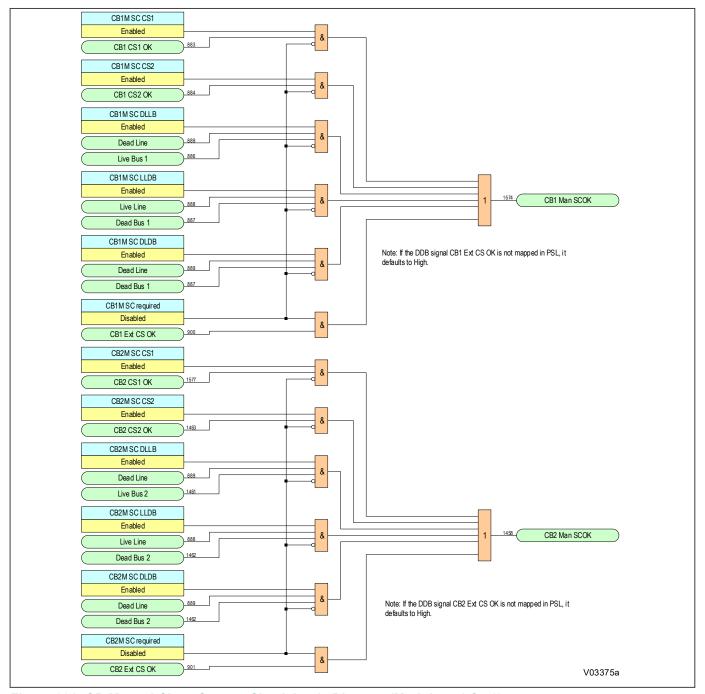

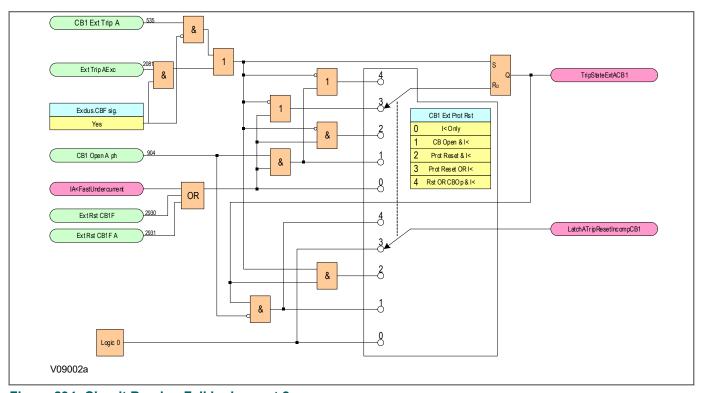

| 12.4.1               | Circuit Breaker Fail Logic - Part 1                                        | 432        |

| 12.4.2               | Circuit Breaker Fail Logic - Part 2                                        | 433        |

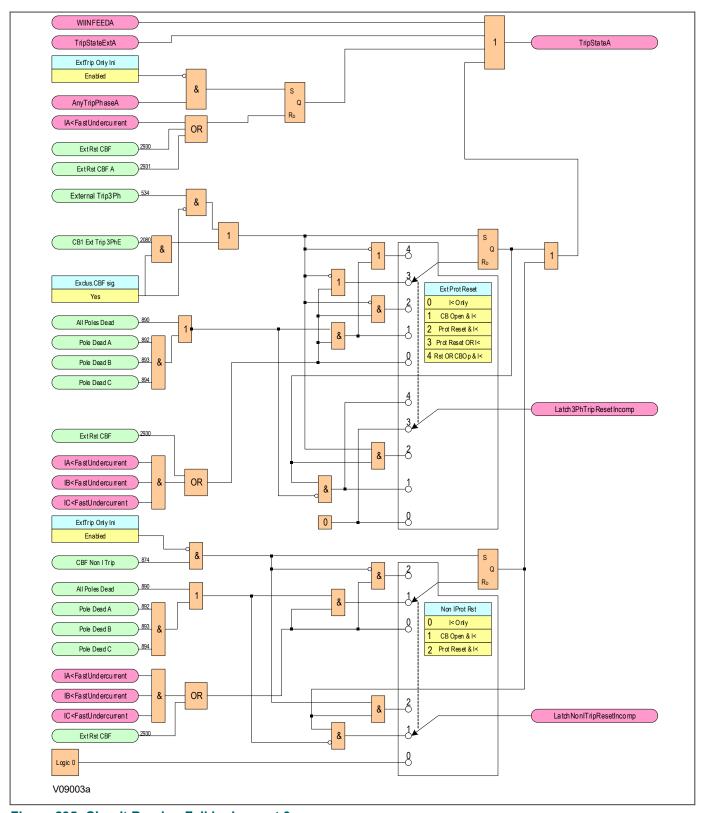

| 12.4.3               | Circuit Breaker Fail Logic - Part 2                                        | 433        |

| 12.4.4               | Circuit Breaker Fail Logic - Part 3                                        | 434        |

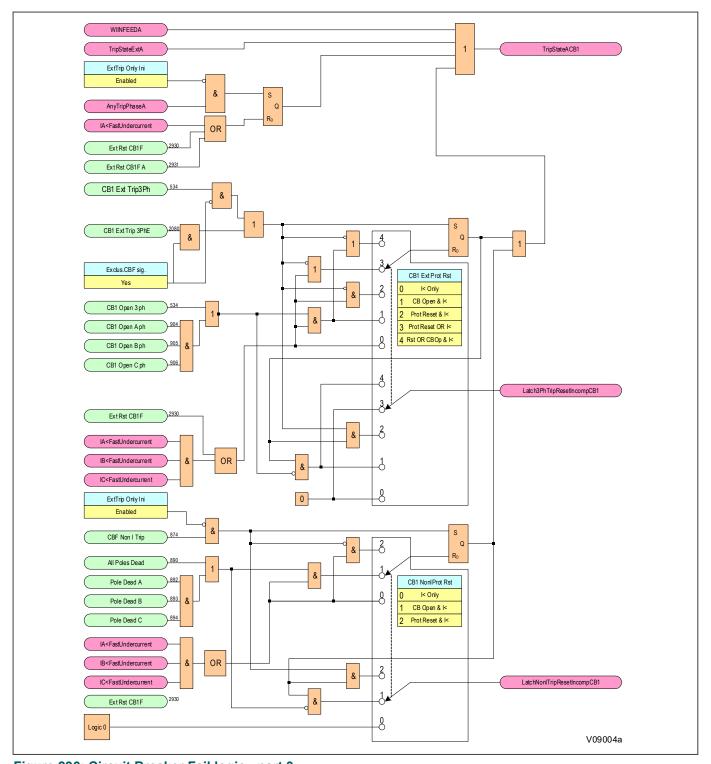

| 12.4.5               | Circuit Breaker Fail Logic - Part 3                                        | 435        |

| 12.4.6               | Circuit Breaker Fail Logic - Part 4                                        | 436        |

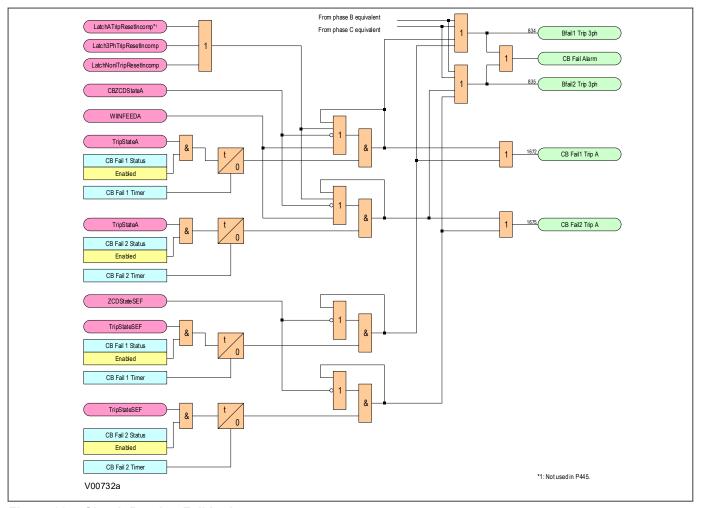

| 12.4.7               | Circuit Breaker Fail Logic - Part 4  Circuit Breaker Fail Logic - Part 4   | 437        |

| 12.7.1               | On ball broaker i all Logic - i all +                                      | 437        |

x P54-TM-EN-2

| 12.5                 | Application Notes                                                                                 | 438        |

|----------------------|---------------------------------------------------------------------------------------------------|------------|

| 12.5.1               | Reset Mechanisms for CB Fail Timers                                                               | 438        |

| 12.5.2               | Setting Guidelines (CB fail Timer)                                                                | 438        |

| 12.5.3               | Setting Guidelines (Undercurrent)                                                                 | 439        |

| Chapte               | er 13 Current Protection Functions                                                                | 441        |

| 13.1                 | Chapter Overview                                                                                  | 442        |

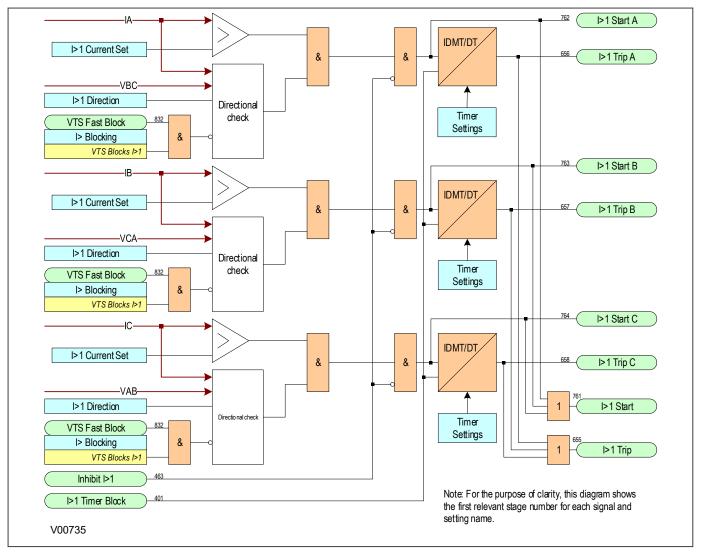

| 13.2                 | Phase Fault Overcurrent Protection                                                                | 443        |

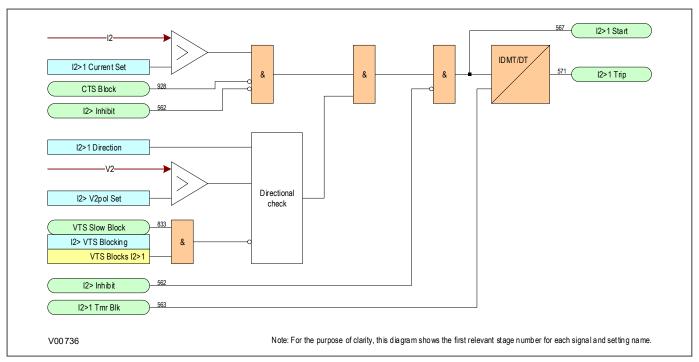

| 13.2.1               | POC Implementation                                                                                | 443        |

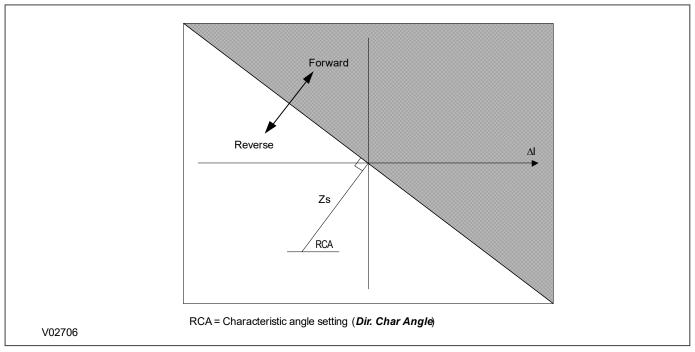

| 13.2.2               | Directional Element                                                                               | 443        |

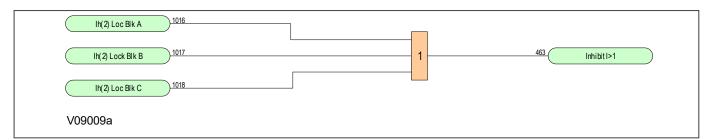

| 13.2.3<br>13.2.4     | POC Logic POC Logic                                                                               | 445<br>445 |

| 13.2.4<br>13.3       | · · · · · · · · · · · · · · · · · · ·                                                             | 445<br>446 |

| 13.3.1               | Negative Sequence Overcurrent Protection  Negative Sequence Overcurrent Protection Implementation | 446        |

| 13.3.1               | Directional Element                                                                               | 446        |

| 13.3.3               | NPSOC Logic                                                                                       | 447        |

| 13.3.4               | Application Notes                                                                                 | 447        |

| 13.3.4.1             | Setting Guidelines (Current Threshold)                                                            | 447        |

| 13.3.4.2             | Setting Guidelines (Time Delay)                                                                   | 447        |

| 13.3.4.3             | Setting Guidelines (Directional element)                                                          | 448        |

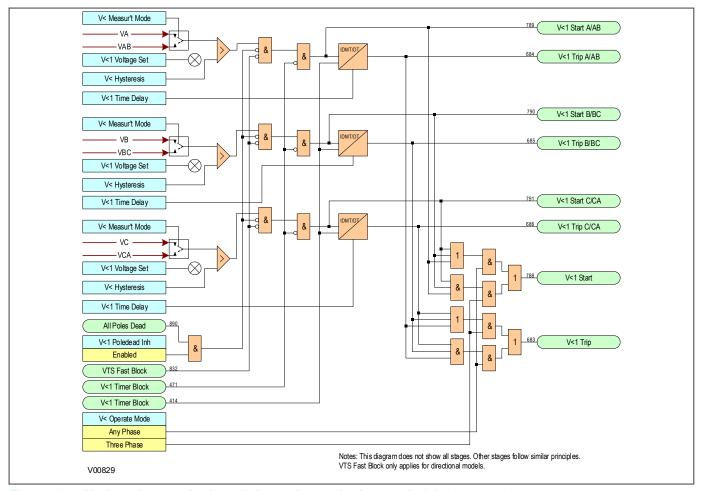

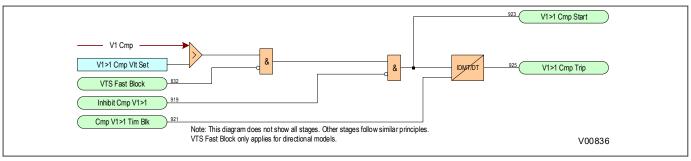

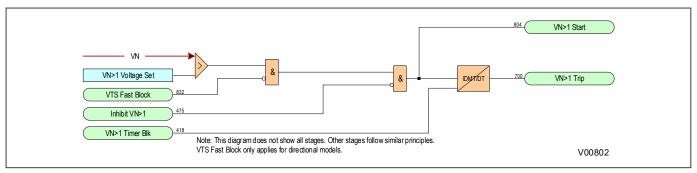

| 13.4                 | Earth Fault Protection                                                                            | 449        |

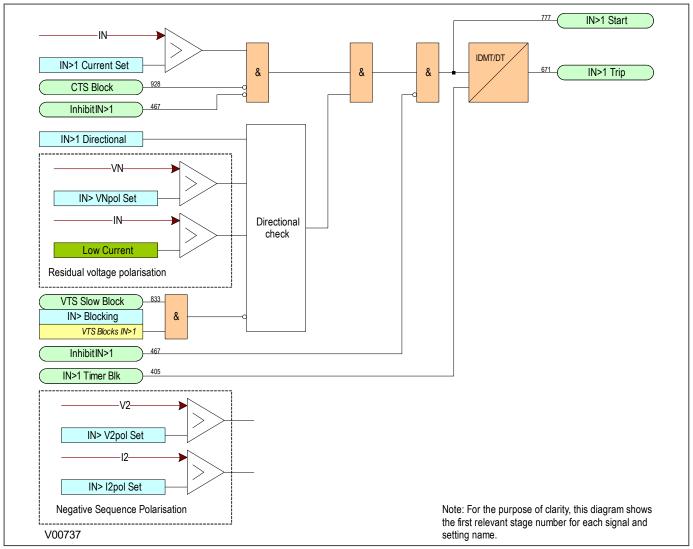

| 13.4.1               | Earth Fault Protection Implementation                                                             | 449        |

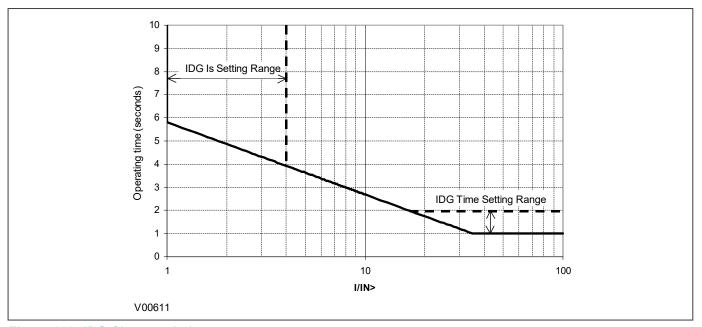

| 13.4.2               | IDG Curve                                                                                         | 449        |

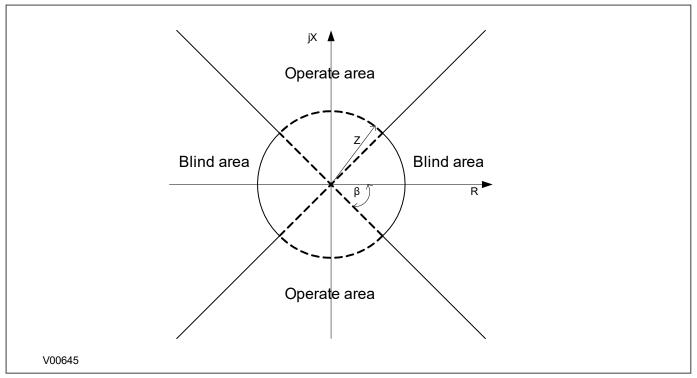

| 13.4.3               | Directional Element                                                                               | 450        |

| 13.4.3.1             | Residual Voltage Polarisation                                                                     | 450        |

| 13.4.3.2             | Negative Sequence Polarisation                                                                    | 451        |

| 13.4.4               | Earth Fault Protection Logic                                                                      | 452        |

| 13.4.5               | Application Notes                                                                                 | 452        |

| 13.4.5.1             | Residual Voltage Polarisation Setting Guidelines                                                  | 452        |

| 13.4.5.2             | Setting Guidelines (Directional Element)                                                          | 452        |

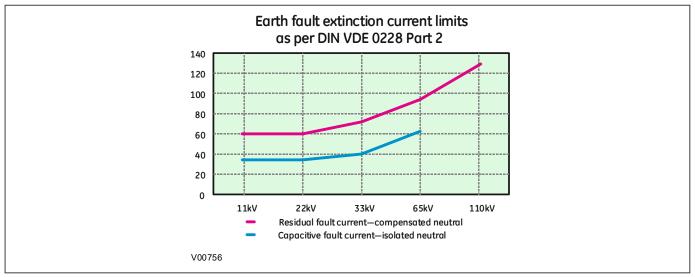

| 13.5                 | Sensitive Earth Fault Protection                                                                  | 454        |

| 13.5.1               | SEF Protection Implementation                                                                     | 454        |

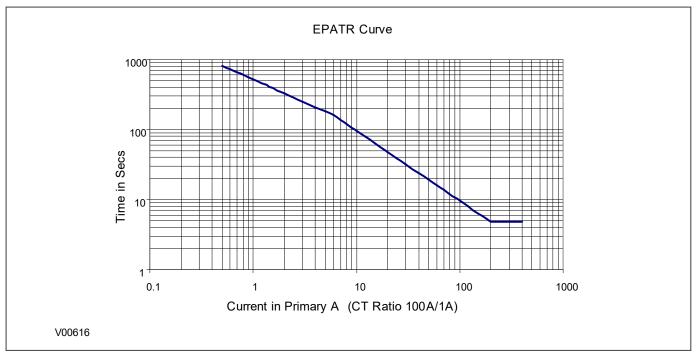

| 13.5.2               | EPATR B Curve                                                                                     | 454        |

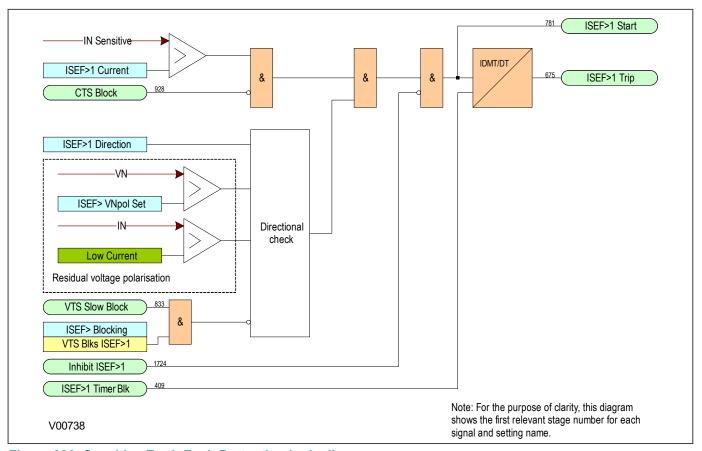

| 13.5.3<br>13.5.4     | Sensitive Earth Fault Protection Logic                                                            | 455<br>456 |

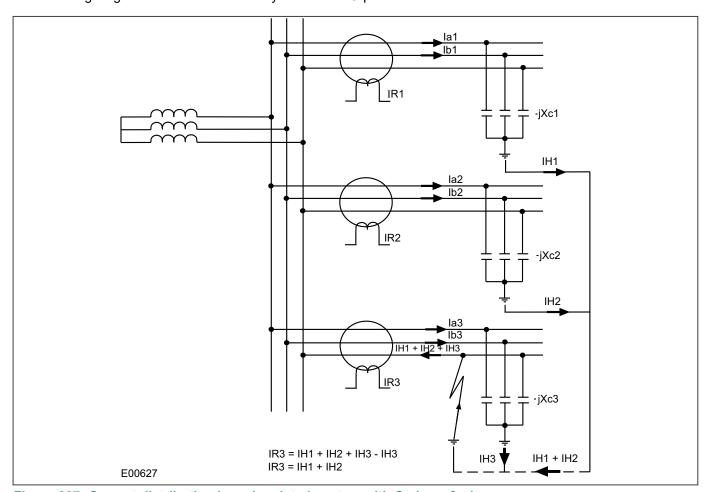

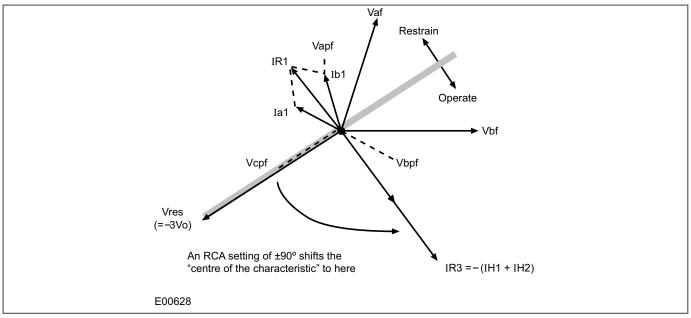

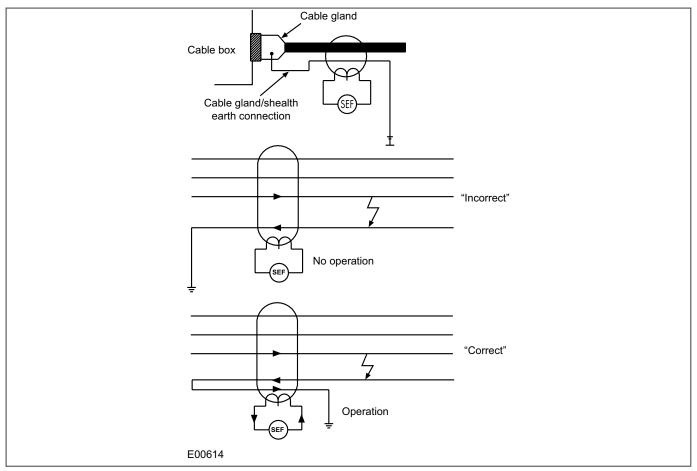

| 13.5.4.1             | Application Notes Insulated Systems                                                               | 456        |

| 13.5.4.2             | Setting Guidelines (Insulated Systems)                                                            | 457        |

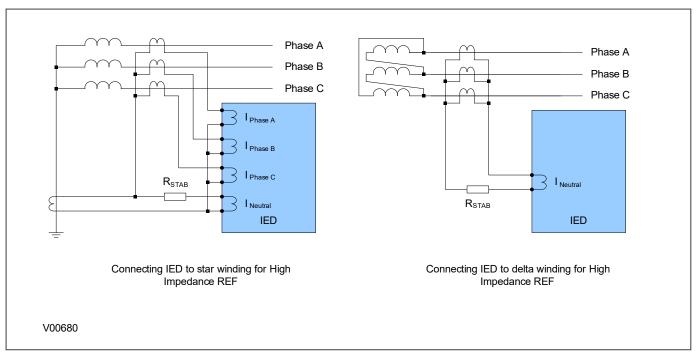

| 13.6                 | High Impedance REF                                                                                | 459        |

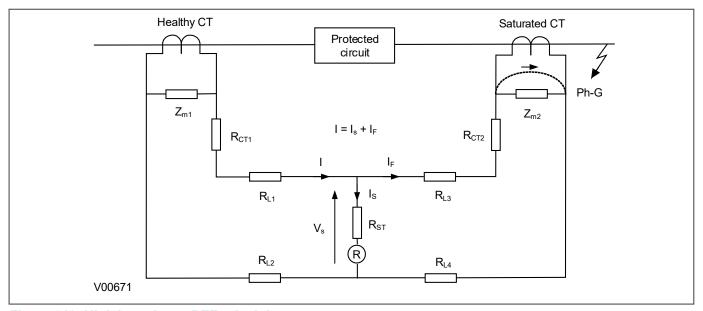

| 13.6.1               | High Impedance REF Principle                                                                      | 459        |

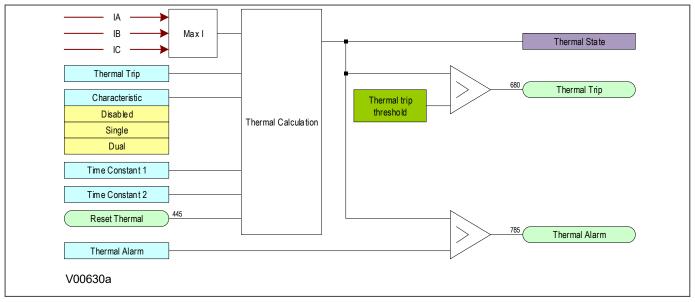

| 13.7                 | Thermal Overload Protection                                                                       | 461        |

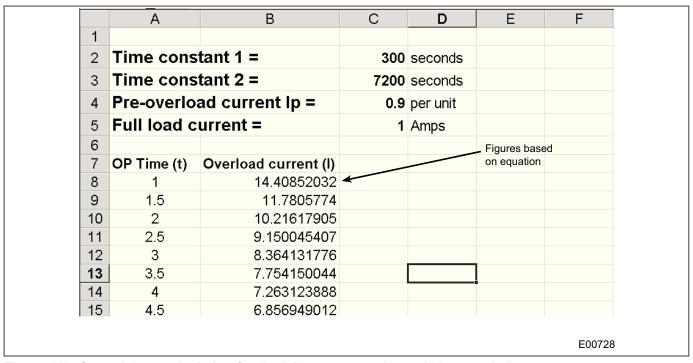

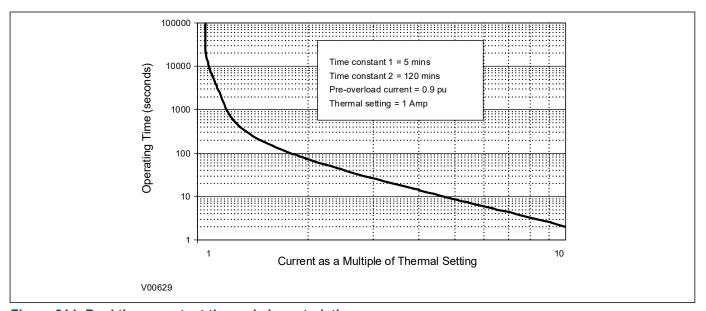

| 13.7.1               | Single Time Constant Characteristic                                                               | 461        |

| 13.7.2               | Dual Time Constant Characteristic                                                                 | 461        |

| 13.7.3               | Thermal Overload Protection Implementation                                                        | 462        |

| 13.7.4               | Thermal Overload Protection Logic                                                                 | 462        |

| 13.7.5               | Application Notes                                                                                 | 462        |

| 13.7.5.1             | Setting Guidelines for Dual Time Constant Characteristic                                          | 462        |

| 13.7.5.2             | Setting Guidelines for Single Time Constant Characteristic                                        | 464        |

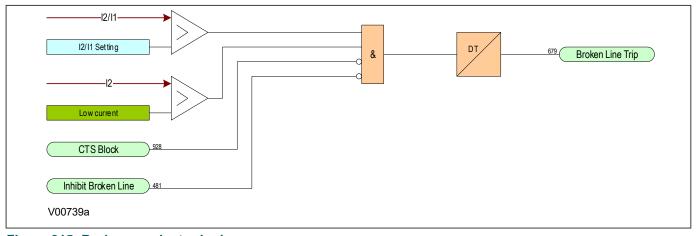

| 13.8                 | Broken Conductor Protection                                                                       | 465        |

| 13.8.1               | Broken Conductor Protection Implementation                                                        | 465        |

| 13.8.2               | Broken Conductor Protection Logic                                                                 | 465        |

| 13.8.3               | Application Notes                                                                                 | 465        |

| 13.8.3.1             | Setting Guidelines                                                                                | 465        |

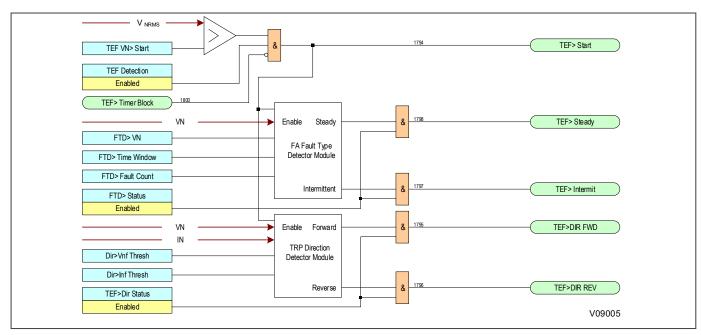

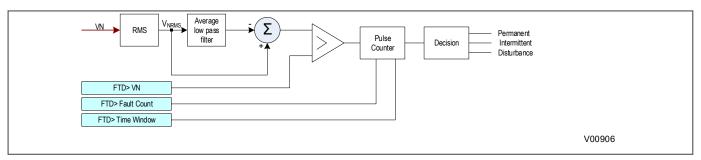

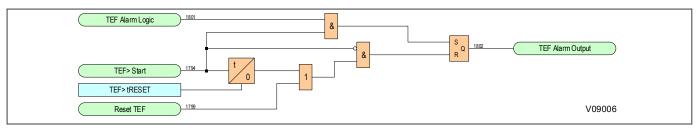

| 13.9                 | Transient Earth Fault Detection                                                                   | 467        |

| 13.9.1               | Transient Earth Fault Detection Implementation                                                    | 468<br>468 |

| 13.9.1.1<br>13.9.1.2 | Transient Earth Fault Detector Fault Type Detector                                                | 468        |

| 10.3.1.∠             | i auit Type Detector                                                                              | 400        |

P54-TM-EN-2 xi

| Contents              |                                                                          | P54               |

|-----------------------|--------------------------------------------------------------------------|-------------------|

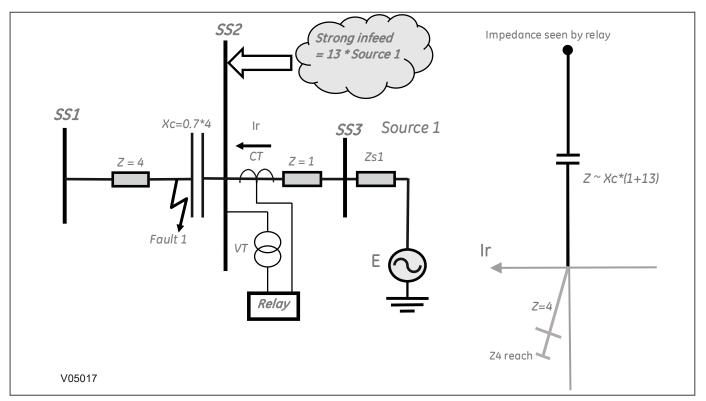

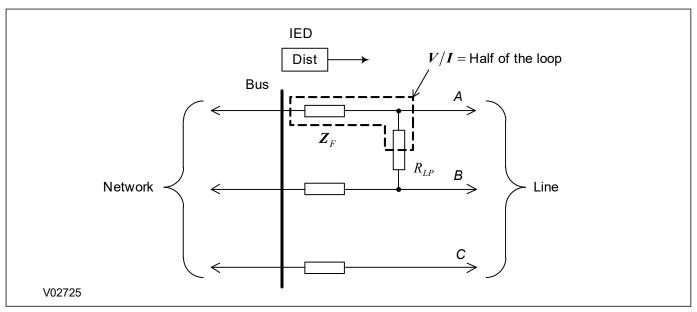

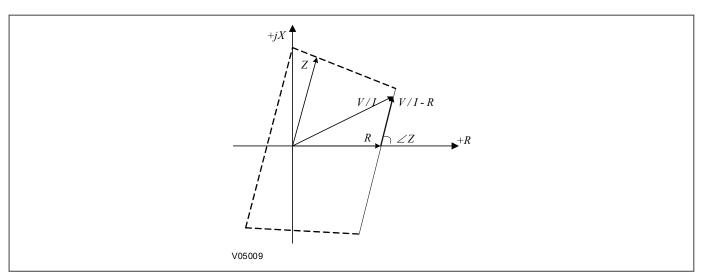

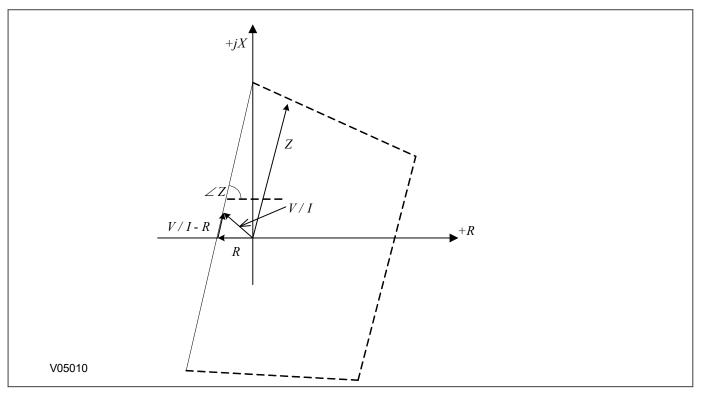

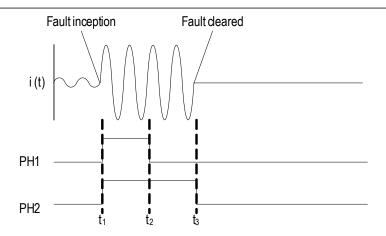

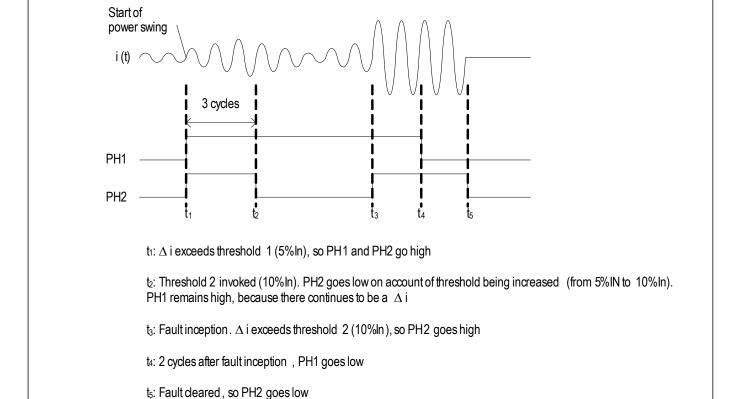

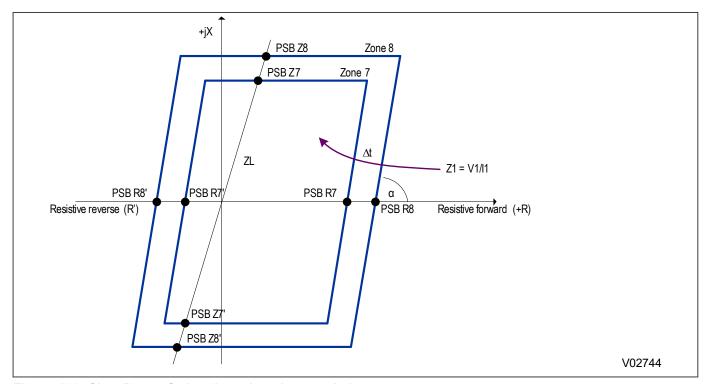

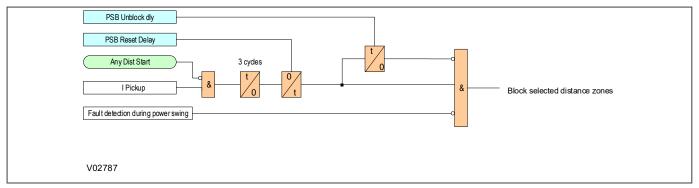

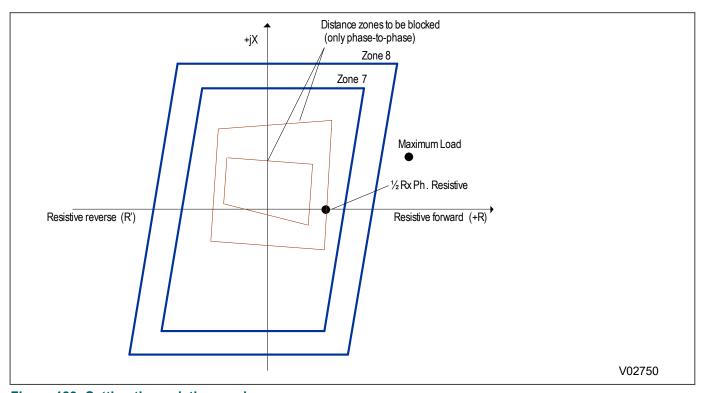

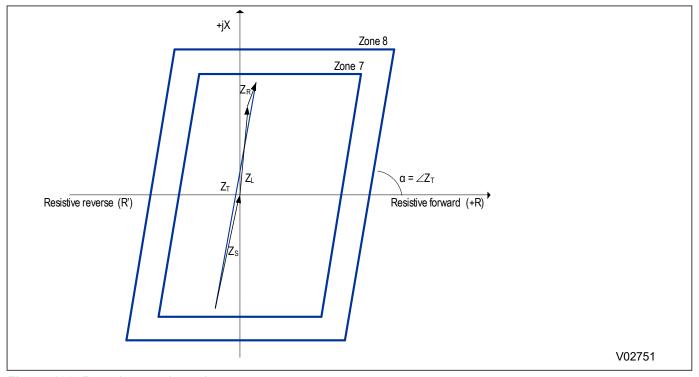

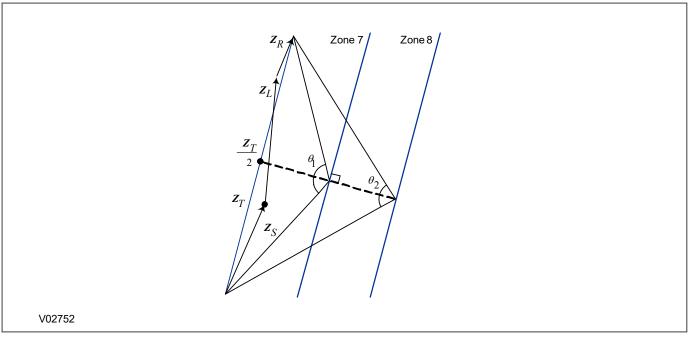

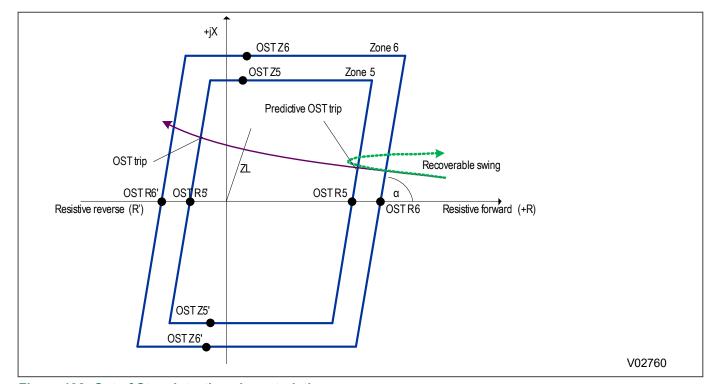

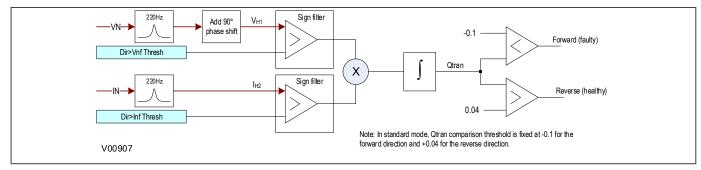

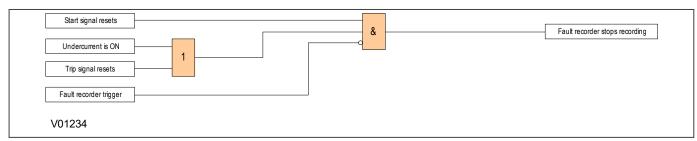

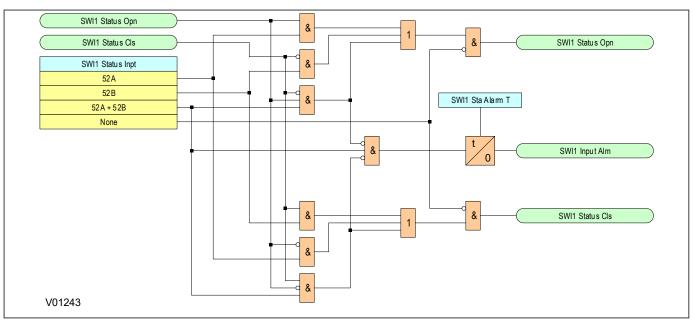

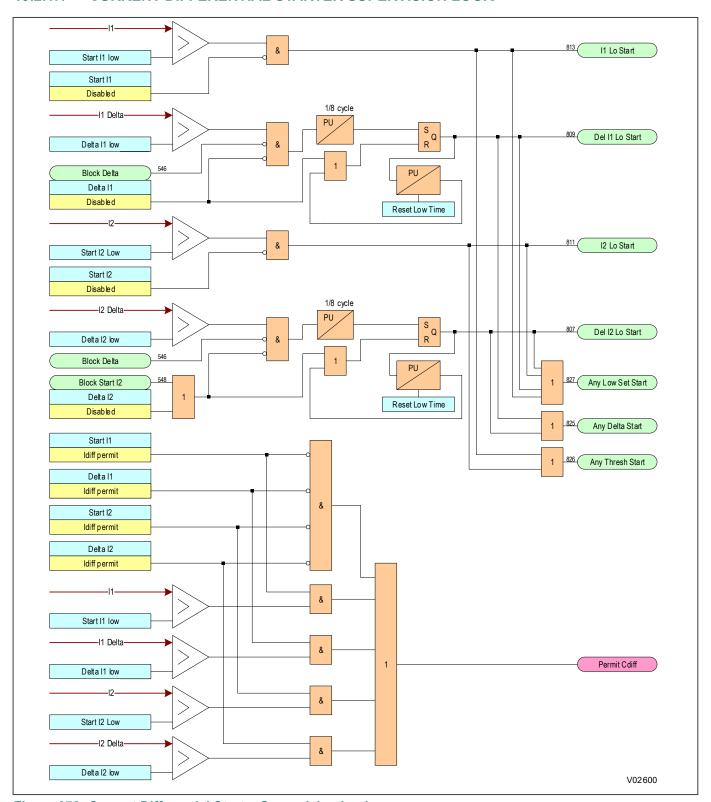

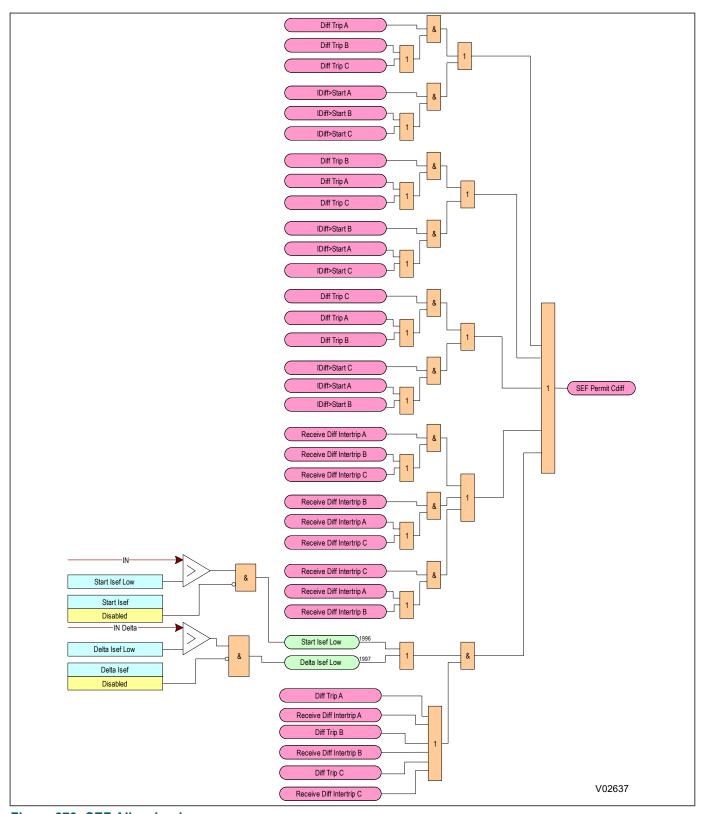

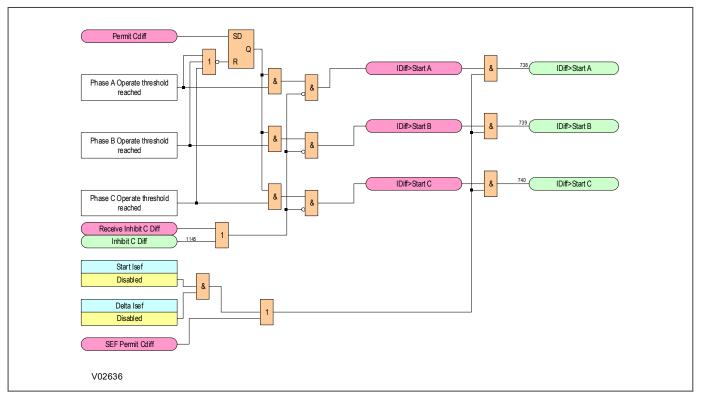

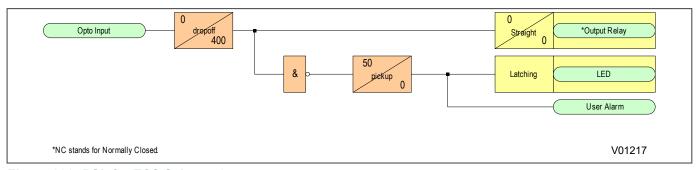

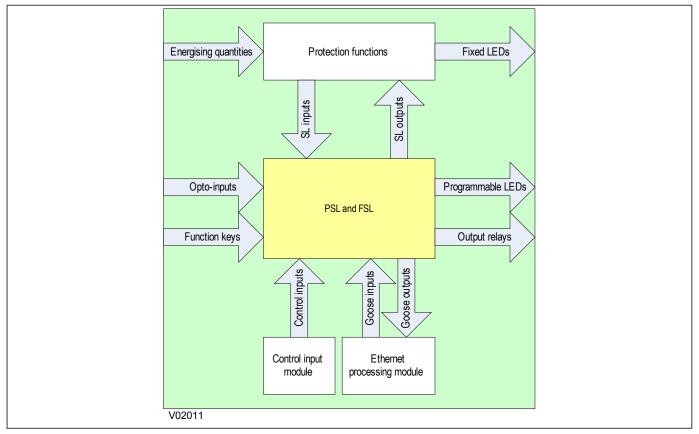

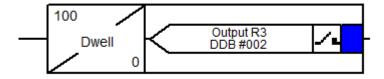

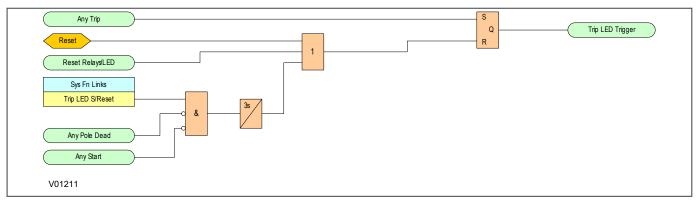

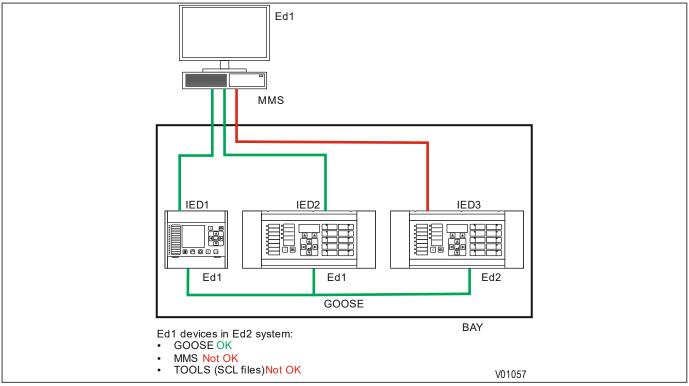

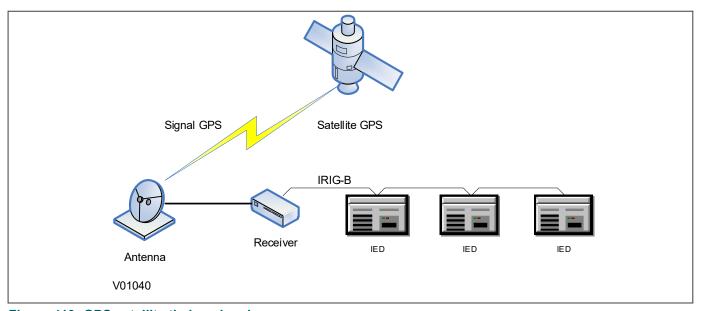

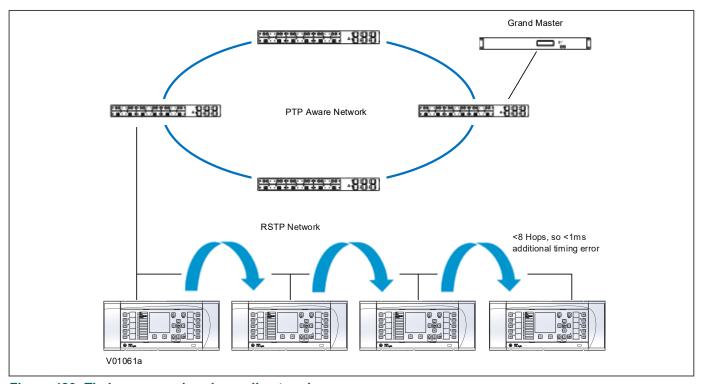

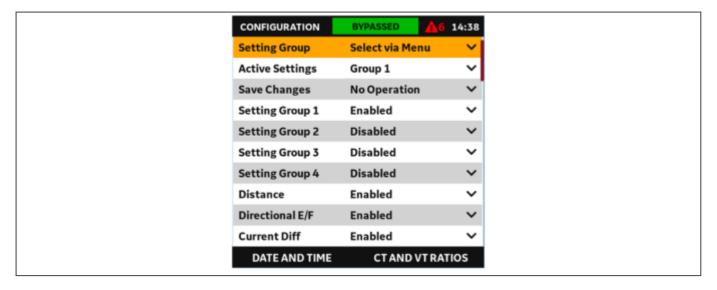

| 13.9.1.3              | Direction Detector                                                       | 468               |